### **Master Informatics Eng.**

2018/19

A.J.Proença

### From ILP to Multithreading

(most slides are borrowed)

AJProença, Advanced Architectures, MiEI, UMinho, 2018/19

1

### Processor arch: beyond Instruction-Level Parallelism

#### XX

- When exploiting ILP, goal is to minimize CPI

- > Pipeline CPI (efficient to exploit loop-level parallelism) =>

- Ideal pipeline CPI +

- Structural stalls +

- Data hazard stalls +

- Control stalls +

- Memory stalls ... cache techniques ✓...

- Multiple issue =>

- find enough parallelism to keep pipeline(s) occupied

- Multithreading =>

- ➤ find additional ways to keep pipeline(s) occupied

- Insert data parallelism features ...(next set of slides)

## **Multiple Issue and Static Scheduling**

■ To achieve CPI < 1, need to complete multiple instructions per clock cycle

### Solutions:

- statically scheduled superscalar processors

- VLIW (very long instruction word) processors

- dynamically scheduled superscalar processors

Copyright © 2012, Elsevier Inc. All rights reserved.

Multiple Issue and Static Scheduling

## **Multiple Issue**

| Common name                  | lssue<br>structure | Hazard<br>detection   | Scheduling               | Distinguishing<br>characteristic                                          | Examples                                                                                   |

|------------------------------|--------------------|-----------------------|--------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Superscalar<br>(static)      | Dynamic            | Hardware              | Static                   | In-order execution                                                        | Mostly in the<br>embedded space:<br>MIPS and ARM,<br>including the ARM<br>Cor∮tex A8, Atom |

| Superscalar<br>(dynamic)     | Dynamic            | Hardware              | Dynamic                  | Some out-of-order execution, but no speculation                           | None at the present                                                                        |

| Superscalar<br>(speculative) | Dynamic            | Hardware              | Dynamic with speculation | Out-of-order execution with speculation                                   | Intel Core i3, i5, i7;<br>AMD Phenom; IBM<br>Power 7                                       |

| VLIW/LIW                     | Static             | Primarily<br>software | Static                   | All hazards determined<br>and indicated by compiler<br>(often implicitly) | Most examples are in signal processing, such as the TI C6x                                 |

| EPIC                         | Primarily static   | Primarily<br>software | Mostly static            | All hazards determined<br>and indicated explicitly<br>by the compiler     | Itanium                                                                                    |

EPIC: Explicitly Parallel Instruction Computer

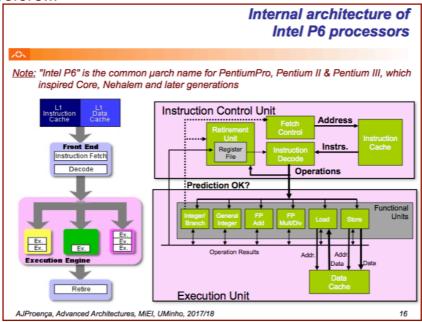

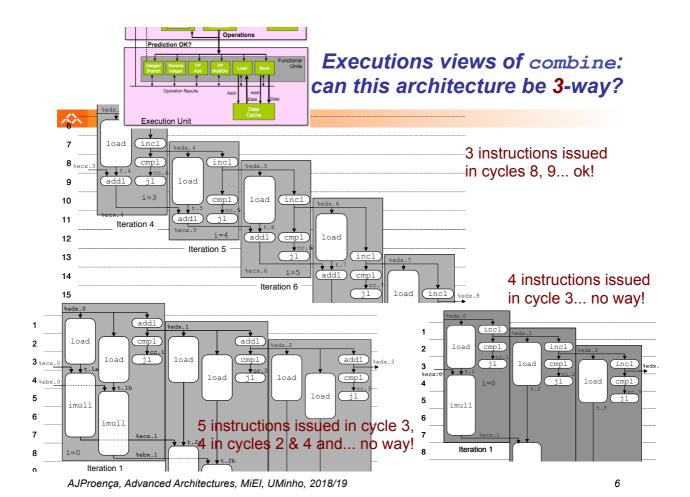

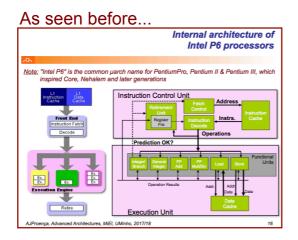

# The n-way superscalar P6: how this architecture supports n-way multiple issue

人入

As seen before...

AJProença, Advanced Architectures, MiEI, UMinho, 2018/19

5

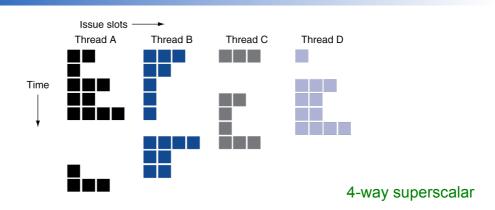

## Multithreading

- Performing multiple threads of execution in parallel

- Replicate registers, PC/IP, etc.

- Fast switching between threads

- Fine-grain multithreading / time-multiplexed MT

- Switch threads after each cycle

- Interleave instruction execution

- If one thread stalls, others are executed

- Coarse-grain multithreading

- Only switch on long stall (e.g., L2-cache miss)

- Simplifies hardware, but doesn't hide short stalls (eg, data hazards)

Chapter 7 — Multicores, Multiprocessors, and Clusters — 7

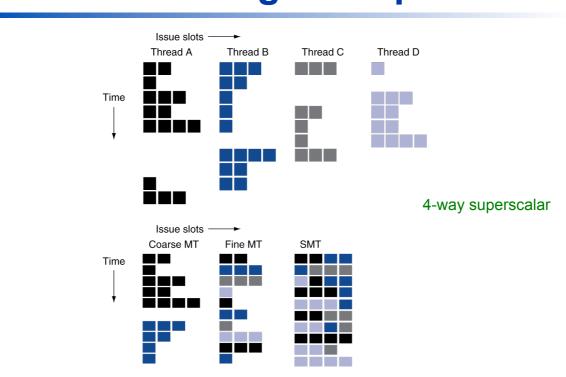

## Simultaneous Multithreading

- In multiple-issue dynamically scheduled processor

- Schedule instructions from multiple threads

- Instructions from independent threads execute when function units are available

- Within threads, dependencies handled by scheduling and register renaming

- Example: Intel Pentium-4 HT

- Two threads: duplicated registers, shared function units and caches

**HT**: Hyper-Threading, Intel trade mark for their SMT implementation MT in Xeon Phi KNC: 4-way SMT with time-mux MT, **not HT**!

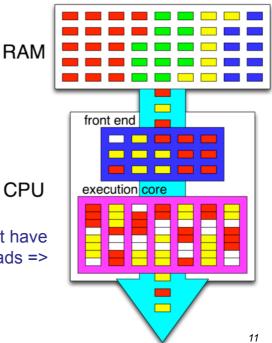

## **Multithreading Example**

Chapter 7 — Multicores, Multiprocessors, and Clusters — 9

## **Multithreading Example**

Hyper-threading

From Wikipedia, the free encyclopedia

众人

The pipelined functional units might have better use if shared among more threads =>

Note: white boxes are bubbles...

AJProença, Advanced Architectures, MiEI, UMinho, 2018/19

### Reading suggestions (from CAQA 5th Ed)

|   | ı | ۹ | ۹ |   |

|---|---|---|---|---|

| 7 | ۱ | Z | ř | ` |

| • | Concepts and challenges in ILP:                                              | section | 3.1  |

|---|------------------------------------------------------------------------------|---------|------|

| • | Exploiting ILP w/ multiple issue & static sche                               | duling: | 3.7  |

| • | Exploiting ILP w/ dyn sched, multiple issue &                                | specul: | 3.8  |

| • | Multithread: exploiting TLP on uniprocessors                                 | :       | 3.12 |

| • | Multiprocessor cache coherence and snooping coherence protocol with example: |         | 5.2  |

| • | Basics on directory-based cache coherence:                                   |         | 5.4  |

| • | Models of memory consistency:                                                |         | 5.6  |

|   |                                                                              |         |      |

A tutorial by Sarita Ave & K. Gharachorloo (see link at website)