# Performance Analysis Guide for Intel® Core™ i7 Processor and Intel® Xeon™ 5500 processors

By Dr David Levinthal PhD. Version 1.0 INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Intel® Hyper-Threading Technology requires a computer system with an Intel® processor supporting Hyper-Threading Technology and an Intel® HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information, see

http://www.intel.com/technology/hyperthread/index.htm; including details on which processors support Intel HT Technology.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel, Pentium, Intel Xeon, Intel NetBurst, Intel Core Solo, Intel Core Duo, Intel Core 2 Duo, Intel Core 2 Extreme, Intel Pentium D, Itanium, Intel SpeedStep, MMX, Intel Atom, and VTune are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting <a href="Intel">Intel</a>'s Web Site.

Copyright © 2008-2009 Intel Corporation

| Introduction                                                                                              | 4    |

|-----------------------------------------------------------------------------------------------------------|------|

| Basic Intel® Core™ i7 Processor and Intel® Xeon™ 5500 Processor Architecture                              | and  |

| Performance Analysis                                                                                      | 5    |

| Core Out of Order Pipeline                                                                                | 6    |

| Core Memory Subsystem                                                                                     | 8    |

| Uncore Memory Subsystem                                                                                   | . 10 |

| Overview                                                                                                  | . 10 |

| Intel® Xeon <sup>TM</sup> 5500 Processor                                                                  | 10   |

| Core Performance Monitoring Unit (PMU)                                                                    | 12   |

| Uncore Performance Monitoring Unit (PMU)                                                                  | 13   |

| Performance Analysis and the Intel® Core™ i7 Processor and Intel® Xeon™ 5500                              |      |

| processor Performance Events: Overview                                                                    | 13   |

| Cycle Accounting and Uop Flow                                                                             | . 14 |

| Branch mispredictions, Wasted Work, Misprediction Penalties and UOP Flow                                  | 17   |

| Stall Decomposition Overview                                                                              | . 20 |

| Measuring Penalties                                                                                       | 21   |

| Core Precise Events                                                                                       | 23   |

| Overview                                                                                                  | 23   |

| Precise Memory Access Events                                                                              | 23   |

| Latency Event                                                                                             | 26   |

| Precise Execution Events                                                                                  | . 28 |

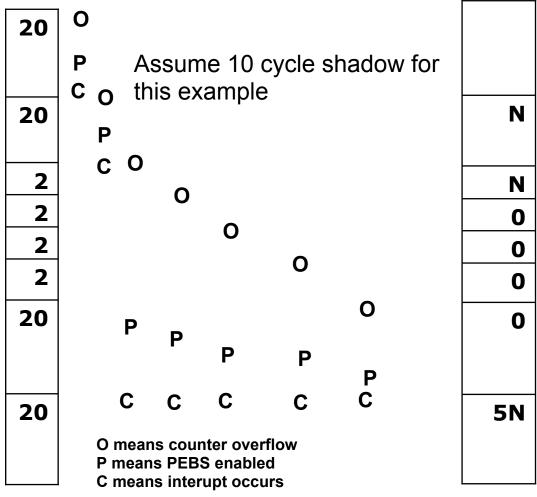

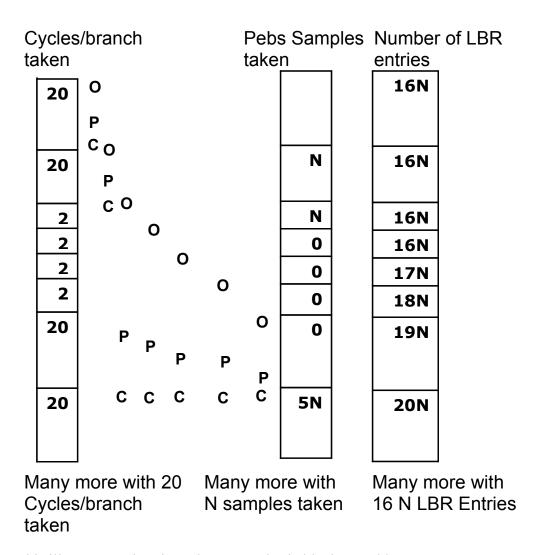

| Shadowing                                                                                                 | 29   |

| Loop Tripcounts                                                                                           | 30   |

| Last Branch Record (LBR)                                                                                  | . 30 |

| Non-PEBS Core Memory Access Events                                                                        | 35   |

| Bandwidth per core                                                                                        | 37   |

| L1D, L2 Cache Access and More Offcore events                                                              | 38   |

| Store Forwarding                                                                                          | . 42 |

| Front End Events                                                                                          | 43   |

| Branch Mispredictions                                                                                     | . 43 |

| FE Code Generation Metrics                                                                                | . 44 |

| Microcode and Exceptions.                                                                                 | . 45 |

| Uncore Performance Events                                                                                 | . 45 |

| The Global Queue                                                                                          | . 46 |

| L3 CACHE Events                                                                                           |      |

| Intel® QuickPath Interconnect Home Logic (QHL)                                                            | 52   |

| Integrated Memory Controller (IMC)                                                                        |      |

| Intel® QuickPath Interconnect Home Logic Opcode Matching                                                  | . 56 |

| Measuring Bandwidth From the Uncore                                                                       |      |

| Conclusion:                                                                                               | . 64 |

| Intel® Core <sup>TM</sup> i7 Processors and Intel® Xeon <sup>TM</sup> 5500 Processors open a new class of |      |

| performance analysis capablitlies                                                                         | . 64 |

| Appendix 1                                                                                                |      |

| Profiles                                                                                                  | . 64 |

| General Exploration                                                                                       | 64   |

| Branch Analysis                         | 65 |

|-----------------------------------------|----|

| Cycles and Uops                         |    |

| Memory Access                           | 66 |

| False- True Sharing                     | 66 |

| FE Investigation                        |    |

| Working Set                             |    |

| Loop Analysis with call sites           | 67 |

| Client Analysis with/without call sites | 68 |

| Appendix II PMU Programming             | 70 |

### Introduction

With the introduction of the Intel® Core<sup>TM</sup> i7 processor and Intel® Xeon<sup>TM</sup> 5500 processors, mass market computing enters a new era and with it a new need for performance analysis techniques and capabilities. The performance monitoring unit (PMU) of the processor has progressed in step, providing a wide variety of new capabilities to illuminate the code interaction with the architecture.

In this paper I will discuss the basic performance analysis methodology that applies to Intel® Core<sup>TM</sup> i7 processor and platforms that support Non-Uniform Memory Access (NUMA) using two Intel® Xeon 5500 processors based on the same microarchitecture as Intel® Core<sup>TM</sup> i7 processor. The events and methodology that referred to Intel® Core<sup>TM</sup> i7 processor also apply to Intel® Xeon<sup>TM</sup> 5500 processors which are based on the same microarchitecture as Intel® Core<sup>TM</sup> i7 processor. Thus statements made only about Intel® core<sup>TM</sup> i7 processors in this document also apply to the Intel® Xeon<sup>TM</sup> 5500 processor based systems. This will start with extensions to the basic cycle accounting methodology outlined for Intel® Core<sup>TM</sup>2 processors(1) and also include both the specific NUMA directed capabilities and the large extension to the precise event based sampling (PEBS).

Software optimization based on performance analysis of large existing applications, in most cases, reduces to optimizing the code generation by the compiler and optimizing the memory access. This paper will focus on this approach. Optimizing the code generation by the compiler requires inspection of the assembler of the time consuming parts of the application and verifying that the compiler generated a reasonable code stream. Optimizing the memory access is a complex issue involving the bandwidth and latency capabilities of the platform, hardware and software prefetching efficiencies and the virtual address layout of the heavily accessed variables. The memory access is where the NUMA nature of the Intel® Core<sup>TM</sup> i7 processor based platforms becomes an issue.

Performance analysis illuminates how the existing invocation of an algorithm executes. It allows a software developer to improve the performance of that invocation. It does not offer much insight about how to change an algorithm, as that really requires a better understanding of the problem being solved rather than the performance of the existing solution. That being said, the performance gains that can be achieved on a large

existing code base can regularly exceed a factor of 2, (particularly in HPC) which is certainly worth the comparatively small effort required.

# Basic Intel® Core™ i7 Processor and Intel® Xeon™ 5500 Processor Architecture and Performance Analysis

Performance analysis on a micro architecture is the experimental investigation of the micro architecture's response to a given instruction and data stream. As such, a reasonable understanding of the micro architecture is required to understand what is actually being measured with the performance events that are available.

This section will cover the basics of the Intel® Core™ i7 processor and Intel® Xeon™ 5500 processor architecture. It is not meant to be complete but merely the briefest of introductions. For more details the reader should consult the Software Developers Programming Optimization Guide. This introduction is broken into sections as

- 1) Overview

- 2) Core out of order pipeline

- 3) Core memory subsystem

- 4) Uncore overview

- 5) Last Level Cache and Integrated memory controller

- 6) Intel® QuickPath Interconnect (Intel QPI)

- 7) Core and Uncore PMUs

#### Overview

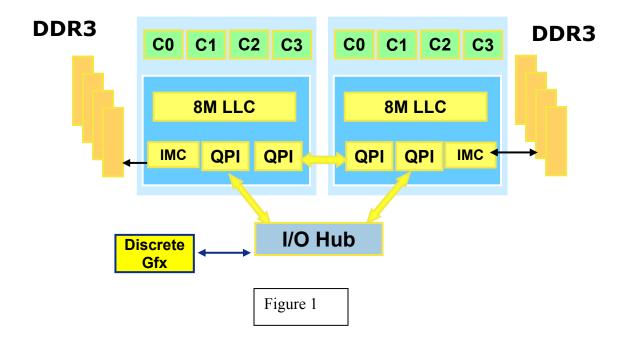

The Intel® Core™ i7 Processor and Intel® Xeon™ 5500 processors are multi core, Intel® Hyper-Threading Technology (HT) enabled designs. Each socket has one to eight cores, which share a last level cache (L3 CACHE), a local integrated memory controller and an Intel® QuickPath Interconnect. Thus a 2 socket platform with quad core sockets might be drawn as:

Each core is quite similar to that of the Intel® Core<sup>TM</sup>2 processor. The pipelines are rather similar except that the Intel® Core<sup>TM</sup> i7 core and pipeline supports Intel® Hyper-Threading Technology (HT), allowing the hardware to interleave instructions of two threads during execution to maximize utilization of the core's resources. The Intel® Hyper-Threading Technology (HT) can be enabled or disabled through a bios setting. Each core has a 32KB data and instruction cache, a 256 KB unified mid-level cache and 2 level DTLB system of 64 and 512 entries. There is a single, 32 entry large page dtlb. The cores in a socket share an inclusive last level cache. The inclusive aspect of this cache is an important issue and will be discussed later. In the usual DP configuration the shared, inclusive last level cache is 8MB and 16 way associative.

The <u>cache coherency protocol messages</u>, between the multiple sockets, are exchanged over the <u>Intel® QuickPath Interconnects</u>. The inclusive L3 CACHE allow this protocol to be extremely fast, <u>with the latency to the L3 CACHE</u> of the adjacent socket being even <u>less than the latency to the local memory</u>.

One of the main virtues of the integrated memory controller is the separation of the cache coherency traffic and the memory access traffic. This enables an enormous increase in memory access bandwidth. This results in a non-uniform memory access (NUMA). The latency to the memory dimms attached to a remote socket is considerably longer than to the local dimms. A second advantage is that the memory control logic can run at processor frequencies and thereby reduce the latency.

The development of a reasonably hierarchical structure and usage of the performance events will require a fairly detailed knowledge of exactly how the components of Intel® Core<sup>TM</sup> i7 processor execute an application's stream of instructions and delivers the required data. What follows is a minimal introduction to these components.

## **Core Out of Order Pipeline**

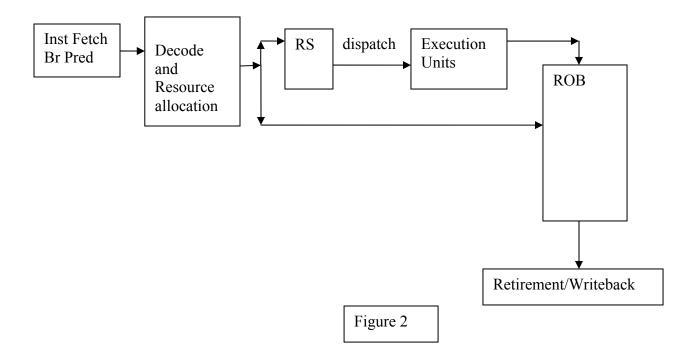

The basic analysis methodology starts with an accounting of the cycle usage for execution. The out of order execution can be considered from the perspective of a simple block diagram as shown below:

After instructions are decoded into the executable micro operations (uops), they are assigned their required resources. They can only be **issued** to the downstream stages when there are sufficient free resources. This would include (among other requirements):

- 1) space in the Reservation Station (RS), where the uops wait until their inputs are available

- 2) space in the Reorder Buffer, where the uops wait until they can be retired

- 3) sufficient load and store buffers in the case of memory related uops (loads and stores)

**Retirement** and write back of state to visible registers is only done for instructions and uops that are on the correct execution path. Instructions and uops of incorrectly predicted paths are flushed upon identification of the misprediction and the correct paths are then processed. Retirement of the correct execution path instructions can proceed when two conditions are satisfied

- 1) The uops associated with the instruction to be retired have completed, allowing the retirement of the entire instruction, or in the case of instructions that generate very large number of uops, enough to fill the retirement window

- 2) Older instructions and their uops of correctly predicted paths have retired The mechanics of following these requirements ensures that the visible state is always consistent with in-order execution of the instructions.

The "magic" of this design is that if the oldest instruction is blocked, for example waiting for the arrival of data from memory, younger independent instructions and uops, whose inputs are available, can be **dispatched** to the **execution** units and warehoused in the ROB upon completion. They will then retire when all the older work has completed.

The terms "<u>issued</u>", "<u>dispatched</u>", "<u>executed</u>" and "<u>retired</u>" have very precise meanings as to where in this sequence they occur and are used in the event names to help document what is being measured.

In the Intel® Core<sup>TM</sup> i7 Processor, the reservation station has 36 entries which are shared between the Hyper-threads when that mode (HT) is enabled in the bios, with some entries reserved for each thread to avoid locking. If not, all 36 could be available to the single running thread, making restarting a blocked thread inefficient. There are 128 positions in the reorder buffer, which are again divided if HT is enabled or entirely available to the single thread if HT is not enabled. As on Core<sup>TM</sup>2 processors, the RS dispatches the uops to one of 6 dispatch ports where they are consumed by the execution units. This implies that on any cycle between 0 and 6 uops can be dispatched for execution.

The hardware branch prediction requests the bytes of instructions for the predicted code paths from the 32KB L1 instruction cache at a maximum bandwidth of 16 bytes/cycle. Instructions fetches are always 16 byte aligned, so if a hot code path starts on the 15<sup>th</sup> byte, the FE will only receive 1 byte on that cycle. This can aggravate instruction bandwidth issues. The instructions are referenced by virtual address and translated to physical address with the help of a 128 entry instruction translation lookaside buffer (ITLB). The x86 instructions are decoded into the processors uops by the pipeline front end. Four instructions can be decoded and issued per cycle.

If the branch prediction hardware mispredicts the execution path, the uops from the incorrect path which are in the instruction pipeline are simply removed where they are, without stalling execution. This reduces the cost of branch mispredictions. Thus the "cost" associated with such mispredictions is only the wasted work associated with any of the incorrect path uops that actually got dispatched and executed and any cycles that are idle while the correct path instructions are located, decoded and inserted into the execution pipeline.

## Core Memory Subsystem

In applications working with large data footprints, memory access operations can dominate the application's performance. Consequently a great deal of effort goes into the design and instrumentation of the data delivery subsystem. Data is organized as a contiguous string of bytes and is transferred around the memory subsystem in cachelines of 64 bytes.

Generally, load operations copy contiguous subsets of the cachelines to registers, while store operations copy the contents of registers back into the local copies of the cachelines. SSE streaming stores are an exception as they create local copies of cachelines which are then used to overwrite the versions in memory, thus are slightly different. The local copies of the lines that are accessed in this way are kept in the 32KB L1 data cache. The access latency to this cache is 4 cycles.

While the program references data through virtual addresses, the hardware identifies the cachelines by the physical addresses. The translation between these two mappings is maintained by the operating system in the form of translation tables. These tables list the translations of the standard 4KB aligned address ranges called pages. They also handle any large pages that the application might have allocated. When a translation is used it is

kept in the data translation lookaside buffers (DTLBs) for future reuse, as all load and store operations require such a translation to access the data caches. Programs reference virtual addresses but access the cachelines in the caches through the physical addresses. As mentioned before, there is a multi level TLB system in each core for the 4KB pages. The level 1 caches have TLBs of 64 and 128 entries respectively for the data and instruction caches. There is a shared 512 entry second level TLB. There is a 32 entry DTLB for the large 2/4MB pages should the application allocate and access any large pages. There are 7 large page ITLB entries per HT. When a translation entry cannot be found in the DTLBs the hardware page walker (HPW) works with the OS translation data structures to retrieve the needed translation and updates the DTLBs. The hardware page walker begins its search in the cache for the table entry and then can continue searching in memory if the page containing the entry required is not found.

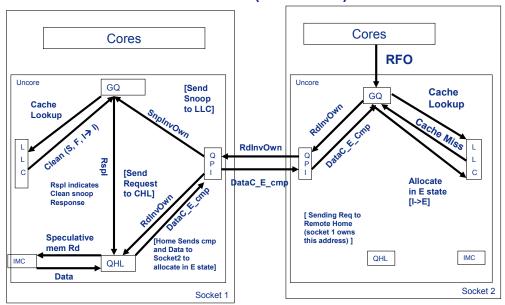

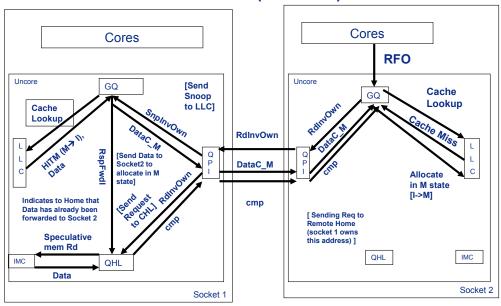

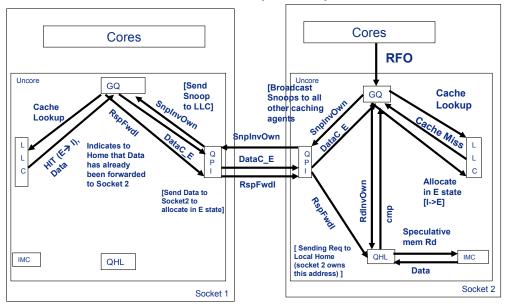

Cacheline coherency in a multi core multi socket system must be maintained to ensure that the correct values for the data variables can be retrieved. This has traditionally been done through the use of a 4 value state for each copy of each cacheline. The four state (MESI) cacheline protocol allows for a coherent use of data in a multi-core, multi-socket platform. A line that is only read can be shared and the cacheline access protocol supports this by allowing multiple copies of the cacheline to coexist in the multiple cores. Under these conditions, the multiple copies of the cacheline would be in what is called a Shared state (S). A cacheline can be put in an Exclusive state (E) in response to a "read for ownership" (RFO) in order to store a value. All instructions containing a lock prefix will result in a (RFO) since they always result in a write to the cache line. The F0 lock prefix will be present in the opcode or is implied by the xchg and cmpxchg instructions when a memory access is one of the operands. The exclusive state ensures exclusive access of the line. Once one of the copies is modified the cacheline's state is changed to Modified (M). That change of state is propagated to the other cores, whose copies are changed to the Invalid state (I).

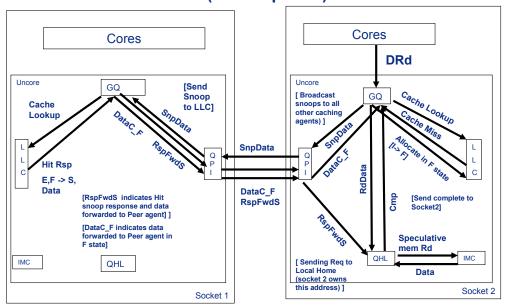

With the introduction of the <u>Intel® QuickPath</u> Interconnect protocol the 4 MESI states are supplemented with a fifth, Forward (F) state, for lines forwarded <u>from on socket to</u> another.

When a cacheline, required by a data access instruction, cannot be found in the L1 data cache it must be retrieved from a higher level and longer latency component of the memory access subsystem. Such a cache miss results in an invalid state being set for the cacheline. This mechanism can be used to count cache misses.

The L1D miss creates an entry in the 16 element superqueue and allocates a line fill buffer. If the line is found in the 256KB mid level cache (MLC, also referred to as L2), it is transferred to the L1 data cache and the data access instruction can be serviced. The load latency from the L2 CACHE is 10 cycles, resulting in a performance penalty of around 6 cycles, the difference of the effective L2 CACHE and L1D latencies. If the line is not found in the L2 CACHE, then it must be retrieved from the uncore.

When all the line fill buffers are in use, the data access operations in the load and store buffers cannot be processed. They are thus <u>queued up in the load and store buffers</u>. When all the load or store buffers are occupied, the front end is inhibited from issuing uops to the RS and OOO engine. This is the same mechanism as used in Core<sup>TM</sup>2 processors to maintain pipeline consistency.

The Intel® Core<sup>TM</sup> i7 processor has a 4 component hardware prefetcher very similar to that of the Core<sup>TM</sup> processors. Two components associated with the L2 CACHE and two components associated with the L1 data cache. The 2 components of L2 CACHE hardware prefetcher are similar to those in the Pentium<sup>TM</sup> 4 and Core<sup>TM</sup> processors. There is a "streaming" component that looks for multiple accesses in a local address window as a trigger and an "adjacency" component that causes 2 lines to be fetched instead of one with each triggering of the "streaming" component. The L1 data cache prefetcher is similar to the L1 data cache prefetcher familiar from the Core<sup>TM</sup> processors. It has another "streaming" component (which was usually disabled in the bios' for the Core<sup>TM</sup> processors) and a "stride" or "IP" component that detected constant stride accesses at individual instruction pointers. The Intel® Core<sup>TM</sup> i7 processor has various improvements in the details of the hardware pattern identifications used in the prefetchers.

### **Uncore Memory Subsystem**

#### Overview

The "uncore" is essentially a shared last level cache (L3 CACHE), a memory access chipset (Northbridge), and a socket interconnection interface integrated into the multi processor package. Cacheline access requests (i.e. L2 Cache misses, uncacheable loads and stores) from the cores are serviced and the multi socket cacheline coherency is maintained with the other sockets and the I/O Hub.

There are five basic configurations of the Intel® Core<sup>TM</sup> i7 processor uncore.

- 1. Intel® Xeon<sup>TM</sup> 550 processor has a 3 channel integrated memory controller (IMC), 2 Intel® QuickPath Interconnects to support up to a DP configuration and an 8 MB L3 CACHE. This is the main focus of this document

- 2. Intel® Core™ i7 processor-HEDT (High End Desk Top) has a 3 channel IMC, 1 Intel® QuickPath Interconnect to access the chipset and an 8 MB L3 CACHE. This is for UP configurations

- 3. A quad core mainstream configuration with a 2 channel IMC, integrated PCI-e and an 8MB L3 CACHE

- 4. A dual core mainstream configuration where the memory access is through an off die chipset to enable support of more memory dimm formats equipped with a 4MB L3 CACHE

- 5. The 8-core implementation based on the Nehalem microarchitecture will be the MP configuration. This will be described in later documents.

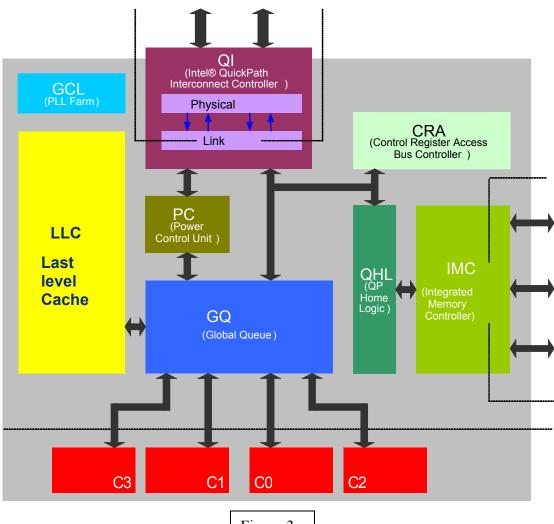

#### Intel® Xeon™ 5500 Processor

IA block diagram of the Intel® Xeon<sup>TM</sup> 5500 processor package is shown below:

Figure 3

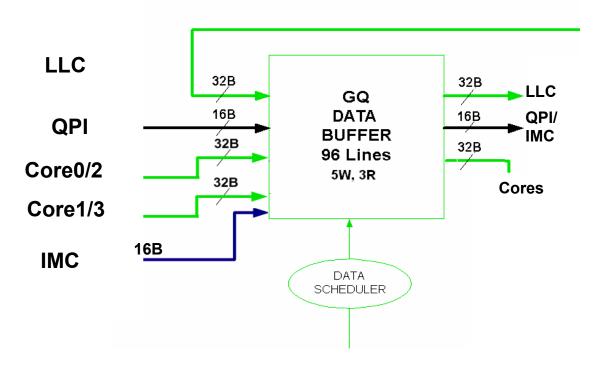

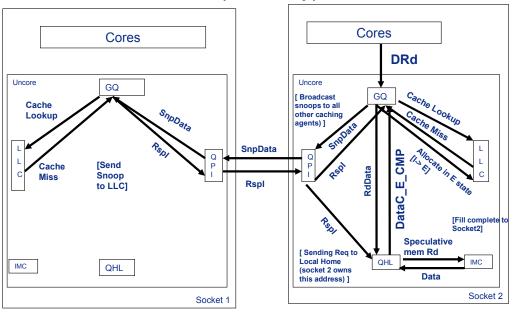

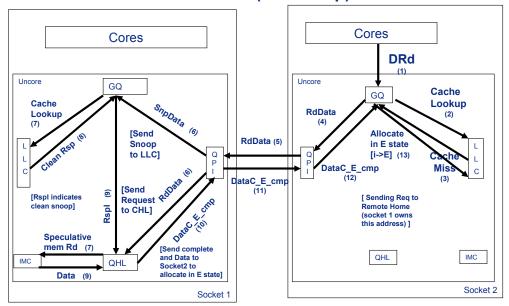

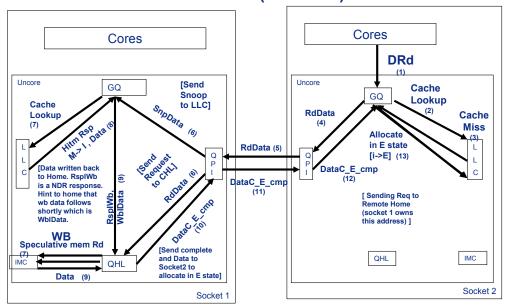

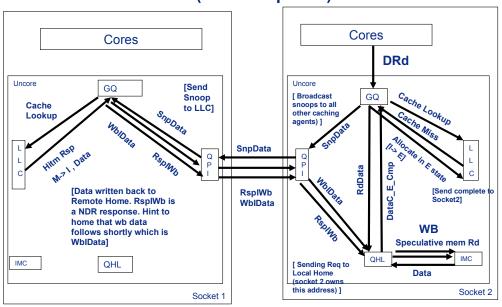

Cacheline requests from the cores or from a remote package or the I/O Hub are handled by the Intel® Xeon<sup>TM</sup> 5500 processor Uncore's Global Queue (GQ). The GQ contains 3 request queues for this purpose. One for writes with 16 entries and one of 12 entries for off package requests delivered by the Intel® QuickPath Interconnect and one of 32 entries for load requests from the cores.

On receiving a cacheline request from one of the cores, the GQ first checks the Last Level Cache (L3 CACHE) to see if the line is on the package. As the L3 CACHE is inclusive, the answer can be quickly ascertained. If the line is in the L3 CACHE and was owned by the requesting core it can be returned to the core from the L3 CACHE directly. If the line is being used by multiple cores, the GQ will snoop the other cores to see if there is a modified copy. If so the L3 CACHE is updated and the line is sent to the requesting core. In the event of an L3 CACHE miss the GQ must send out requests for the line. Since the cacheline could be in the other package, a request through the Intel® QuickPath Interconnect (Intel QPI) to the remote L3 CACHE must be made. As each Intel® Core<sup>TM</sup> i7 processor package has its own local integrated memory controller the GQ must identify the "home" location of the requested cacheline from the physical address. If the address identifies home as being on the local package, then the GQ makes a simultaneous request

to the local memory controller, the Integrated memory controller (IMC). If home is identified as belonging to the remote package, the request sent by the QPI will also be used to access the remote IMC.

This process can be viewed in the terms used by the Intel® QuickPath Interconnect protocol. Each socket has a Caching agent (that might be thought of as the GQ plus the L3 CACHE) and a Home agent (the IMC). An L3 CACHE miss results in simultaneous queries for the line from all the Caching Agents and the Home agent (wherever it is). This is shown diagrammatically below for a system with 3 caching agents (2 sockets and an I/O hub) none of whom have the line and a home agent, which ultimately delivers the line to the caching agent C that requested it.

Request

SnpData

SnpData

SnpData

SnpData

Rsp

DataC\_E\_Cm

Clearly, the IMC has queues for handling local and remote, read and write requests. These will be discussed at greater length as the events that monitor their use are described.

## Core Performance Monitoring Unit (PMU)

Each core has its own PMU. They have 3 fixed counters and 4 general counters for each Hyper-Thread. If HT is disabled in the bios only one set of counters is available. All the core monitoring events count on a per thread basis with one exception that will be discussed. The PMIs are raised on a per logical core or HT basis when HT is enabled. There is a significant expansion of the PEBS events with respect to Intel® Core<sup>TM</sup>2 processors. This will be discussed in detail. The Last Branch Record (LBR) has been expanded to hold 16 source/target pairs for the last 16 taken branch instructions.

## **Uncore Performance Monitoring Unit (PMU)**

The Uncore has its own PMU for monitoring its activity. It consists of 8 general counters and one fixed counter. The fixed counter monitors the uncore frequency, which is different than the core frequency. In order for the uncore PMU to generate an interrupt it must rely on the core PMUs. If an interrupt on overflow is desired, a bit pattern of which core PMUs to signal to raise a PMI must be programmed. As the uncore events have no knowledge of the core, PID or TID that ultimately generated the event, the most reasonable approach to sampling on uncore events requires sending an interrupt signal to all of the core PMUs and generating one PMI per logical core.

## Performance Analysis and the Intel® Core™ i7 Processor and Intel® Xeon™ 5500 processor Performance Events: Overview

The objective of performance analysis is of course to improve an applications performance. The process reveals insights into an existing code base's performance limitations. In general it does not tell the user how to improve an algorithm, merely the limitations in the algorithm the user has already chosen. Improving an algorithm usually requires deeper insight into the problem being solved, rather than insight into how the chosen solution performs.

There are dominantly two types of performance limitations identified through analysis. These are sub optimal code generation and sub optimal interaction of the code and the micro architecture. Performance event profiling with software tools like the VTune<sup>TM</sup> performance analyzer, PTU and such address both issues. A profile of an execution sensitive event like core cycles or instructions (uops) executed identifies which parts of the code are actually being executed and thus dominating the applications performance. One of the primary uses of such tools is as execution sensitive assembly editors. It is the disassembly view of such tools that allow a user to evaluate the code generation and determine if the compilation was optimal, if the high level language encoding results in artificially constraining the compiler's options (false loop dependencies for example), or identifying a compiler's inadequacies. While this is certainly one of the most important aspects of performance analysis, it is not the subject of this paper. The focus here is on the Intel® Core<sup>TM</sup> i7 processor specifics and identifying performance bottlenecks in the applications interaction with the micro architecture.

The spectrum of performance monitoring events on the Intel® Core<sup>TM</sup> i7 processor provides unprecedented insights into and application's interaction with the processor micro architecture. The remainder of this paper will be devoted to describing the systematic use of the performance events. It is divided into the following discussions

- 1) Cycle Accounting and Uop Flow

- 2) Stall Decomposition Overview

- 3) Precise Memory Access Events (PEBS)

- 4) Precise Branch Events (PEBS, LBR)

- 5) Core Memory Access Events (non-PEBS)

- 6) Other Core Events (non-PEBS)

- 7) Front End Issues

#### 8) Uncore Events

## **Cycle Accounting and Uop Flow**

Improving performance starts with identifying where in the application the cycles are spent and identifying how they can be reduced. As Amdahl's law points out, an application can only be sped up by the fraction of cycles that are being used by the section of code being optimized. To accomplish such a cycle count reduction it is critical to know how the cycles are being used. This is both to identify those places where there is nothing to be gained, but more importantly where any effort is most likely to be fruitful. Such a cycle usage decomposition is usually described as cycle accounting. The first step of the decomposition is usually to divide the cycles into two groups, productive and unproductive or "stalled". This is particularly important, as stalled cycles are usually the easiest to recover.

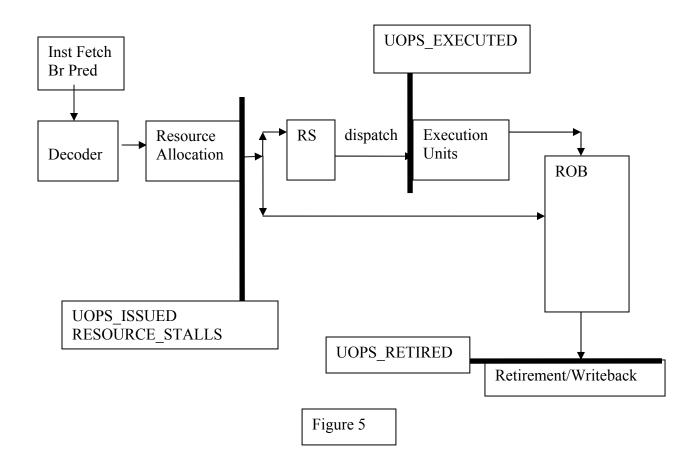

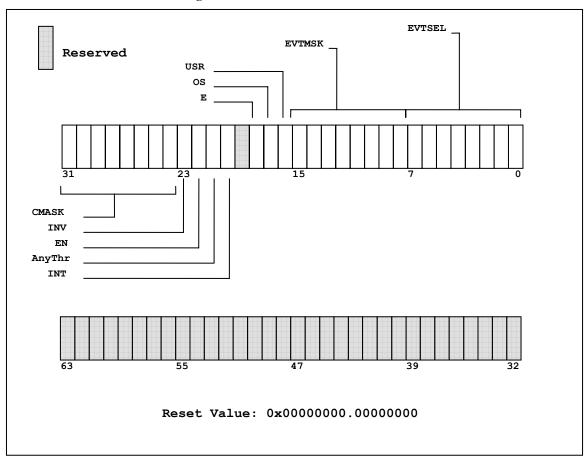

The techniques described here rely on several of the PMU programming options beyond the performance event selection. These include the threshold (:cmask=val), comparison logic (:inv=1), edge detection (:edge=1) and privilege level (:usr=1, :sup=1) filtering being applied to the event counting. When the PMU is programmed to count an event the PerfEvtSel register for one of the 4 programmable counters is programmed with the event code and umask value to select which event should be counted. There are many different programmable conditions under which the event can be counted. These are also controlled by the PerfEvtSel register. When the cmask value is zero the counter is incremented by the value of the event on each cycle. (ex: inst retired.any can have any value from 0 to 4). If the cmask is non zero then the value on each cycle is compared to the cmask value and thus the cycles for which the comparison condition is true are counted. The condition can be either GE (>=) or LT (<), depending on whether the "inv" bit is zero or not. The "edge detect" can be used to count the changing of the condition determined by the cmask, this is used to count divides and sgrt instructions as will be discussed later. There are more details on the PerfEvtSel register in Appendix II. The cycle usage is best evaluated with the flow of uops through the pipeline. In the Intel® Core<sup>TM</sup> i7 processor core there are three particularly valuable places where this can be done. Using the simplified pipeline diagram we identify these three spots as:

- 1) Output of the decoding and resource allocation (issue)

- 2) Execution

- 3) Retirement

On the diagram below we highlight a few of these performance events and where they monitor the uop flow.

The pipeline has buffers distributed along the uops flow path, for example the RS and ROB. The result is the flow discontinuities (stalls) in one location do not necessarily propagate at all locations. The OOO execution can keep the execution units occupied during cycles where no uops retire, with the completed uops simply being staged in the ROB for future retirement. Similarly the buffering in the RS can similarly keep the execution units occupied during short discontinuities in uops being issued by the pipeline front end. The design optimizes the continuity of the uop flow at the dispatch to the execution units. Thus SW performance optimization should also focus on this objective.

In order to evaluate the efficiency of execution, cycles are divided into those where micro-ops are dispatched to the execution units and those where no micro-ops are dispatched, which are thought of as execution stalls. In the Intel®  $Core^{TM}$  if processor (as on the Intel®  $Core^{TM}$  2 processors) uops are dispatched to one of six ports. By comparing the total uop count to 1 (cmask=1) and using a "less than" (inv=1) and "greater than or equal to" (inv = 0) comparison, the PMU can divide all cycles into "stalled" and "unstalled" classes. These PMU programmings are predefined enabling the identify:

Total cycles = UOPS\_EXECUTED.CORE\_STALL\_CYCLES + UOPS\_EXECUTED.CORE\_ACTIVE\_CYCLES

# Where UOPC\_EXECUTED.CORE\_STALL\_CYCLES is defined as UOPS\_EXECUTED:CMASK=1:INV=1, using the usual shorthand notation.

This expression is in a sense a trivial truism, uops either are, or are not, executed on any given cycle. This technique can be applied to any core event, with any threshold (cmask) value and it will always be true. Any event, with a given cmask threshold value, counts the cycles where the events value is >= to the cmask value (inv=0), or < the cmask value (inv=1). Thus the sum of the counts for inv =0 and inv=1 for a non-zero cmask will always be the total core cycles, not just the unhalted cycles. This sum value is of course subject to any frequency throttling the core might experience during the counting period. The choice of dividing cycles at execution in this particular manner is driven by the realization that ultimately keeping the execution units occupied is one of the essential objectives of optimization.

Total cycles can be directly measured with CPU\_CLK\_UNHALTED.TOTAL\_CYCLES. This event is derived from CPU\_CLK\_UNHALTED.THREAD by setting the cmask = 2 and inv = 1, creating a condition that is always true. The difference between these two is the halted cycles. These occur when the OS runs the null process.

The signals used to count the memory access uops executed (ports 2, 3 and 4) are the only core events which cannot be counted on a logical core or HT basis. Thus the total execution stall cycles can only be evaluated on a per core basis. If the HT is disabled this presents no difficulty. There is some added complexity when the HT is enabled however. While the memory ports only count on a per core basis, the ALU ports (0,1,5) count on a per thread basis. The number of cycles where no uops were dispatched on the ALU ports can be evaluated on a per thread basis consequently. This event is called <a href="https://linear.com/uops-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-executed-cycles-execu

<u>UOPS\_EXECUTED.CORE\_STALL\_CYCLES</u> <=

True execution stalls per thread <=

UOPS\_EXECUTED.PORT015\_STALL\_CYCLES

Of course with HT disabled then

UOPS\_EXECUTED.CORE\_STALL\_CYCLES =

True execution stalls per thread

In addition the <u>uop flow can be measured at issue and retirement on a per thread basis</u> and so can the number of cycles where no uops flow at those points. These events are predefined as UOPS\_ISSUED.STALL\_CYCLES for measuring stalls in uop issue and UOPS\_RETIRED.STALL\_CYCLES for measuring stalls in uop retirement, respectively.

The edge detection option in the PMU can be used to count the number of times an event's value changes, by detecting the rising signal edge. If this is applied to UOPS\_EXECUTED.CORE\_STALLS\_CYCLES as, (UOPS\_EXECUTED:CMASK=1:INV=1:EDGE=1), then the PMU will count the number of stalls. This programming is defined as the event UOPS\_EXECUTED.CORE\_STALL\_COUNT. The ratio,

### UOPS\_EXECUTED.CORE\_STALLS\_CYCLES/ UOPS\_EXECUTED.CORE\_STALLS\_COUNT

is the average stall duration, and with the use of sampling can be measured reasonably accurately even within a code region like a single loop.

# Branch mispredictions, Wasted Work, Misprediction Penalties and UOP Flow

Branch mispredictions can introduce execution inefficiencies that are typically decomposed into three components.

- 1) Wasted work associated with executing the uops of the incorrectly predicted path

- 2) Cycles lost when the pipeline is flushed of the incorrect uops

- 3) Cycles lost while waiting for the correct uops to arrive at the execution units In the Intel® Core<sup>TM</sup> i7 processor, there are no execution stalls associated with clearing the pipeline of mispredicted uops (component 2). These uops are simply removed from the pipeline without stalling executions or dispatch. This typically lowers the penalty for mispredicted branches. Further, the penalty associated with instruction starvation (component 3) can be measured for the first time in OOO x86 architectures.

Speculative OOO execution introduces a component of execution inefficiency due to the uops on mispredicted paths being dispatched to the execution units. This represents wasted work as these uops will never be retired as is part of the cost associated with mispredicted branches. It can be found through monitoring the flow of uops through the pipeline. The uop flow can be measured at 3 points in the diagram shown above, going into the RS with the event UOPS\_ISSUED, going into the execution units with UOPS\_EXECUTED and at retirement with UOPS\_RETIRED. The differences of between the upstream measurements and at retirement measure the wasted work associated with these mispredicted uops.

As UOPS\_EXECUTED must be measured per core, rather than per logical core/HT, the wasted work per core is evaluated as

```

Wasted Work = (UOPS_EXECUTED.PORT234_CORE + UOPS_EXECUTED.PORT015 (for HT1) + UOPS_EXECUTED.PORT015 (for HT2) ) - (UOPS_RETIRED.ANY(for HT1) + UOPS_RETIRED.ANY(for HT2) )

```

The events were designed to be used in this manner without corrections for micro or macro fusion. If HT is disabled, the count for the second HT is not needed. A "per thread" measurement can be made looking at the difference between the uops issued and uops retired as both of these events can be counted per logical core/HT. It over counts slightly, by the mispredicted uops that are eliminated in the RS before they can waste cycles being executed, but this is a small correction.

# Wasted Work/thread = (UOPS\_ISSUED.ANY + UOPS\_ISSUED.FUSED) - UOPS\_RETIRED.ANY

As stated above, there is no interruption in uop dispatch or execution due to flushing the pipeline. Thus the second component of the misprediction penalty is zero.

The third component of the misprediction penalty, instruction starvation, occurs when the instructions associated with the correct path are far away from the core and execution is stalled due to a lack of uops. This can now be explicitly measured at the output of the resource allocation as follows. Using a cmask =1 and inv=1 logic applied to UOPS\_ISSUED, we can count the total number of cycles where no uops were issued to the OOO engine.

UOPS\_ISSUED.STALL\_CYCLES = UOPS\_ISSUED.ANY:CMASK=1:INV=1 Since the event RESOURCE\_STALLS.ANY counts the number of cycles where uops could not be issued due to a lack of downstream resources (RS or ROB slots, load or store buffers etc), the difference is the cycles no uops are issued because there were none available.

With HT disabled we can identify an instruction starvation condition indicating that the front end was not delivering uops when the execution stage could have accepted them. Instruction Starvation =

UOPS ISSUED.STALL CYCLES - RESOURCE STALLS.ANY

When HT is enabled, the uop delivery to the RS alternates between the two threads. In an ideal case the above condition would then count 50% of the cycles, as those cycles were delivering uops for the other thread. We can modify the expression by subtracting the cycles that the other thread is having uops issued.

Instruction Starvation =

UOPS\_ISSUED.STALL\_CYCLES - RESOURCE\_STALLS.ANY -UOPS\_ISSUED.ANY:CMASK=1(other thread)

But this will over count as the resource\_stall condition could exist on "this" thread while the other thread was issuing uops. An alternative might be

CPU\_CLK\_UNHALTED.THREAD – UOPS\_ISSUED.CORE\_CYCLES\_ACTIVE-RESOURCE\_STALLS.ANY

Where UOPS\_ISSUED.CORE\_CYCLES\_ACTIVE counts the UOPS\_ISSUED.ANY event with cmask=1 and allthreads=1, thus counting the cycles either thread issues uops. The problem of course is that if the other thread can always issue uops, it will mask the stalls in the thread that cannot.

The event INST\_RETIRED.ANY (instructions retired) is most commonly used to evaluate a cycles/instruction ratio, but the most powerful usage is in evaluating basic block execution counts. All of the instructions in a basic block are retired exactly the same number of times by the very definition of a basic block. As several instructions tend to be retired on each cycle where instructions are retired there tends to be a clustering of the IP values associated with sampling on INST\_RETIRED.ANY. This same clustering also occurs for the cpu cycle counting events. The result is that the distribution of samples in a VTune<sup>TM</sup> Analyzer type disassembly spreadsheet is far from uniform. Frequently there are instructions with no samples at all right next to instructions with

thousands of samples. The solution to this is to average the sample counts over the instructions of the basic block. This will result in yielding the best measurement of the basic block execution count.

Basic Block Execution Count =

$\Sigma_{inst\ in\ BB}$  Samples(inst\_retired)\*Sample\_after\_Value/(Number of inst in BB)

When analyzing the execution of loops, the basic block execution counts can be used to get the average tripcount (iteration count) of the loop. For a simple loop with no conditional branches, this ends up being the ratio of the basic block execution count of the loop block to the basic block execution count of the block immediately before and/or after the loop block. Judicious use of averaging over multiple blocks can be used to improve the accuracy. Usually the objective of the analysis is just to determine if the tripcount is large (> 100) or very small (<10), so this rough technique is usually adequate. There is a fixed counter version of the event and a version that can be programmed into the general counters, which also uses the PEBS (precise event based sampling) mechanism. The PEBS mechanism is armed by the overflow of the counter. There is a short propagation delay between the counter overflow and when PEBS is ready to capture the next event. This shadow makes the use of the precise event inappropriate for basic block execution counting. By far the best mechanism for this is to use the PEBS br inst retired all branches event and capture the LBRs (Last Branch Records). More will be said of the use of the precise version in the section on precise events. A final event should be mentioned in regards to stalled execution. Chains of dependent long latency instructions (fmul, fadd, imul, etc) can result in the dispatch being stalled while the outputs of the long latency instructions become available. In general there are no events that assist in counting such stalls with the exception of the divide and sqrt instructions. For these two instructions the event ARITH can be used to count both the occurrences of these instructions and the duration in cycles that they kept their execution units occupied. The event ARITH CYCLES DIV BUSY counts the cycles that either the divide/sqrt execution unit was occupied. (perhaps the events name is thus a bit misleading)

The flow of uops is mostly due to the decoded instructions. There are also uops that can enter the flow due to micro coded exception handling, like those associated with floating point exceptions. Micro code will be covered as part of the Front End discussion.

In summary, a table of these events is shown below, with C indicating the CMASK value, I indicating the INV value, E indicating the EDGE DETECT value and AT indicating the value of the ALLTHREAD bit. For the Edge Detect to work, a non zero cmask value must also be used.

Table 1

| Event Name            | Definition                                    | Umask | Event        | С | 1 | Ε | AT |

|-----------------------|-----------------------------------------------|-------|--------------|---|---|---|----|

| ARITH.CYCLES_DIV_BUSY | Cycles the divider is busy                    | 1     | 14           | 0 | 0 | 0 | 0  |

| ARITH.DIV             | Divide Operations executed                    | 1     |              | 0 | 0 | 1 | 0  |

| ARITH.MUL             | Multiply operations executed                  | 2     |              | 0 | 0 | 0 | 0  |

| CPU_CLK_UNHALTED.REF  | Reference cycles when<br>thread is not halted | 0     | Fixed<br>Ctr | 0 | 0 | 0 | 0  |

| CPU_CLK_UNHALTED.THREAD                 | Cycles when thread is not halted                                                              |    | 0  | Fixed<br>Ctr | 0 | 0 | 0 | 0 |

|-----------------------------------------|-----------------------------------------------------------------------------------------------|----|----|--------------|---|---|---|---|

| CPU_CLK_UNHALTED.THREAD_P               | Cycles when thread is<br>not halted (programmable counter)<br>Reference cycles when thread is |    | 0  | 3C           | 0 | 0 | 0 | 0 |

| CPU_CLK_UNHALTED.REF_P                  | not halted (programmable counter)                                                             |    | 1  | Fixed        | 0 | 0 | 0 | 0 |

| INST_RETIRED.ANY                        | Instructions retired (fixed counter) Instructions retired                                     |    | 0  | Ctr          | 0 | 0 | 0 | 0 |

| INST_RETIRED.ANY_P                      | (programmable counter)                                                                        |    | 1  | C0           | 0 | 0 | 0 | 0 |

| UOPS_EXECUTED.PORT0                     | Uops dispatched from port 0                                                                   |    | 1  | B1           | 0 | 0 | 0 | 0 |

| UOPS_EXECUTED.PORT1                     | Uops dispatched on port 1                                                                     |    | 2  |              | 0 | 0 | 0 | 0 |

| UOPS_EXECUTED.PORT2_CORE                | Uops dispatched on port 2                                                                     |    | 4  |              | 0 | 0 | 0 | 1 |

| UOPS_EXECUTED.PORT3_CORE                | Uops dispatched on port 3                                                                     |    | 8  |              | 0 | 0 | 0 | 1 |

| UOPS_EXECUTED.PORT4_CORE UOPS EXECUTED. | Uops dispatched on port 4                                                                     |    | 10 |              | 0 | 0 | 0 | 1 |

| PORT5<br>UOPS EXECUTED.                 | Uops dispatched on port 5                                                                     |    | 20 |              | 0 | 0 | 0 | 0 |

| PORT015<br>UOPS_EXECUTED.PORT015        | Uops dispatched on ports 0, 1 or 5<br>Cycles no Uops                                          |    | 40 |              | 0 | 0 | 0 | 0 |

| _STALL_CYCLES UOPS_EXECUTED.            | dispatched on ports 0, 1 or 5                                                                 |    | 40 |              | 1 | 1 | 0 | 0 |

| PORT234_CORE<br>UOPS_EXECUTED.          | Uops dispatched on ports 2, 3 or 4<br>Cycles no Uops                                          |    | 80 |              | 0 | 0 | 0 | 1 |

| CORE_ACTIVE_CYCLES UOPS_EXECUTED.       | dispatched on any port<br>Number of times no Uops                                             | 3F |    |              | 1 | 0 | 0 | 1 |

| CORE_STALL_COUNT<br>UOPS_EXECUTED.      | dispatched on any port<br>Cycles no Uops                                                      | 3f |    |              | 1 | 1 | 1 | 1 |

| CORE_STALL_CYCLES                       | dispatched on any port                                                                        | 3F |    |              | 1 | 1 | 0 | 1 |

| UOPS_ISSUED.ANY                         | Uops issued                                                                                   |    | 1  | 0E           | 0 | 0 | 0 | 0 |

| UOPS_ISSUED.STALL_CYCLES                | Cycles no Uops were issued                                                                    |    | 1  |              | 1 | 1 | 0 | 0 |

| UOPS_ISSUED.FUSED                       | Fused Uops issued                                                                             |    | 2  |              | 0 | 0 | 0 | 0 |

| UOPS_RETIRED.ACTIVE_CYCLES              | Cycles Micro-ops are retiring                                                                 |    | 1  | C2           | 1 | 0 | 0 | 0 |

| UOPS_RETIRED.ANY                        | Micro-ops retired                                                                             |    | 1  |              | 0 | 0 | 0 | 0 |

| UOPS_RETIRED.STALL_CYCLES               | Cycles Micro-ops are not retiring                                                             |    | 1  |              | 1 | 1 | 0 | 0 |

| UOPS_RETIRED.RETIRE_SLOTS               | Number of retirement slots used                                                               |    | 2  |              | 0 | 0 | 0 | 0 |

| UOPS_RETIRED.MACRO_FUSED                | Number of macro-fused Uops retired                                                            |    | 4  |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.ANY                     | Resource related stall cycles                                                                 |    | 1  | A2           | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.LOAD                    | Load buffer stall cycles                                                                      |    | 2  |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.RS_FULL                 | Reservation Station full stall cycles                                                         |    | 4  |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.STORE                   | Store buffer stall cycles                                                                     |    | 8  |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.ROB_FULL                | ROB full stall cycles                                                                         |    | 10 |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.FPCW                    | FPU control word write stall cycles                                                           |    | 20 |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.MXCSR                   | -                                                                                             |    | 40 |              | 0 | 0 | 0 | 0 |

| RESOURCE_STALLS.OTHER                   | Other Resource related stall cycles                                                           |    | 80 |              | 0 | 0 | 0 | 0 |

|                                         |                                                                                               |    |    |              |   |   |   |   |

## **Stall Decomposition Overview**

The decomposition of the stall cycles is accomplished through a standard approximation. It is assumed that the penalties occur sequentially for each performance impacting event. Consequently, the total loss of cycles available for useful work is then the number of events,  $N_i$ , times the average penalty for each type of event,  $P_i$ .

Counted Stall Cycles =

$$\sum P_i * N_i$$

This only accounts for the performance impacting events that are or can be counted with a PMU event. Ultimately there will be several sources of stalls that cannot be counted, however their total contribution can be estimated by the difference of

The unaccounted component can become negative as the sequential penalty model is overly simple and usually over counts the contributions of the individual architectural issues. As UOPS\_EXECUTED.CORE\_STALL\_CYCLES counts on a per core basis rather than on a per thread basis, the over counting can become severe. In such cases it may be preferable to use the port 0,1,5 uop stalls, as that can be done on a per thread basis.

$$\label{eq:counted_thread} \begin{split} & = Stalls/thread - Counted\_Stall\_Cycles/thread \\ & = UOPS\_EXECUTED. \ PORT015\_THREADED\_STALL\_CYCLES \\ & - \sum P_i * N_i \end{split}$$

This unaccounted component is meant to represent the components that were either not counted due to lack of performance events or simply neglected during the data collection.

One can also choose to use the "retirement" point as the basis for stalls. The PEBS UOPS\_RETIRED.STALL\_CYCLES event has the advantage of being evaluated on a per thread basis and being having the HW capture the IP associated with the retiring uop. This means that the IP distribution will not be effected by STI/CLI deferral of interrupts in critical sections of OS kernels, thus producing a more accurate profile of OS activity.

## **Measuring Penalties**

Decomposing the stalled cycles in this manner should always start by first considering the large penalty events, events with penalties of greater than 10 cycles for example. Short penalty events (P < 5 cycles) can frequently be hidden by the combined actions of the OOO execution and the compiler. Both of these strive to create maximal parallel execution for precisely the purpose of keeping the execution units busy during stalls due to instruction dependencies. The large penalty operations are dominated by memory access and the very long latency instructions for divide and sqrt.

The largest penalty events are associated with load operations that require a cacheline which is not in one of the core's two data caches. Not only must we count how many occur, but we need to know what penalty to assign. The standard approach to measuring latency is to measure the average number of cycles a request is in a queue.

$$Latency = (\Sigma_{cycles} \ Queue\_entries\_outstanding)/Queue\_inserts$$

However, the penalty associated with each queue insert (ie cachemiss), is the latency divided by the average queue occupancy. This correction is needed to avoid over counting associated with overlapping penalties.

Average Queue Depth =  $(\Sigma_{cycles} \ Queue\_entries\_outstanding)$ /Cycles\_queue\_not\_empty

Thus

Penalty = Latency/Average Queue Depth = Cycles\_queue\_not\_empty/Queue\_inserts

An alternative way of thinking about this is to realize that the sum of all the penalties, for an event that occupies a queue for its duration, cannot exceed the time that the queue is not empty.

#### Cycles queue not empty >= Events \* <Penalty>

The equality results in the expression derived in the first part of the discussion.

Neither of these more standard techniques will be used much for this processor. In part due to the wide number of data sources and the large variations in their data delivery latencies. The Precise Event Based Sampling (PEBS) will be the technique of choice The use of the precise latency event, that will be discussed later, provides a more accurate and flexible measurement technique when sampling is used. As each sample records both a load to use latency and a data source, the average latency per data source can be evaluated. Further as the PEBS hardware supports buffering the events without generating a PMI until the buffer is full, it is possible to make such an evaluation quite efficient.

While there are many events that will yield the number of L2 CACHE misses, the associated penalties may average over a wide variety of data sources which actually have individual penalties that vary by an order of magnitude. A more detailed decomposition is needed that just an L2 CACHE miss.

The approximate latencies for the individual data sources that respond to an L2 CACHE miss are shown in table 2. These values are only approximate as they depend on processor frequency and DIMM speed among other things.

#### Table 2

| Data Source                               | Latency    |

|-------------------------------------------|------------|

| L3 CACHE hit, line unshared               | ~40 cycles |

| L3 CACHE hit, shared line in another core | ~65 cycles |

| L3 CACHE hit, modified in another core    | ~75 cycles |

|                                           | ~100-300   |

| remote L3 CACHE                           | cycles     |

| Local Dram                                | ~60 ns     |

| Remote Dram                               | ~100 ns    |

NOTE: THESE VALUES ARE ROUGH APPROXIMATIONS. THEY DEPEND ON CORE AND UNCORE FREQUENCIES, MEMORY SPEEDS, BIOS SETTINGS, NUMBERS OF DIMMS, ETC, ETC.. YOUR MILEAGE MAY VARY.

#### **Core Precise Events**

#### Overview

The Precise Event Based Sampling (PEBS) mechanism enables the PMU to capture the architectural state and IP at the completion of the instruction that caused the event. This not only allows the location of the events in the instruction space to be accurate profiled, but by capturing the values of the registers, instruction arguments can be reconstructed in a post processing phase. The Intel® Core<sup>TM</sup> i7 processor has greatly expanded the numbers and types of precise events.

The mechanism works by using the counter overflow to arm the PEBS data acquisition. Then on the next event, the data is captured and the interrupt is raised.

The captured IP value is sometimes referred to as IP +1, because at the completion of the instruction, the IP value is that of the next instruction.

By their very nature precise events must be "at-retirement" events. For the purposes of this discussion the precise events are divided into Memory Access events, associated with the retirement of loads and stores, and Execution Events, associated with the retirement of all instructions or specific non memory instructions (branches, FP assists, SSE uops)

## Precise Memory Access Events

There are two enormously powerful properties common to all precise memory access events:

- 1) The exact instruction can be identified because the hardware captures the IP of the offending instruction. Of course the captured IP is that of the following instruction but one simply moves the samples up one instruction. This works even when the recorded IP points to the first instruction of a basic block because in such a case the offending instruction has to be the last instruction of the previous basic block, as branch instructions never load or store data.

- 2) The PEBS buffer contains the values of all 16 general registers, R1-R16, where R1 is also called RAX. When coupled with the disassembly the address of the load or store can be reconstructed and used for data access profiling. The Intel® Performance Tuning Utility does exactly this, providing a wide variety of powerful analysis techniques.

The Intel® Core™ i7 processor precise memory access events mainly focus on loads as those are the events typically responsible for the very long duration execution stalls. They are broken down by the data source, thereby indicating the typical latency and the data locality in the intrinsically NUMA configurations. These precise load events are the only L2 CACHE, L3 CACHE and DRAM access events that only count loads. All others will also include the L1D and/or L2 CACHE hardware prefetch requests. Many will also include RFO requests, both due to stores and to the hardware prefetchers.

All four general counters can be programmed to collect data for precise events. The ability to reconstruct the virtual addresses of the load and store instructions allows an analysis of the cacheline and page usage efficiency. Even though cachelines and pages are defined by physical address the lower order bits are identical, so the virtual address can be used.

As the PEBS mechanism captures the values of the register at completion of the instruction, the dereferenced address for the following type of load instruction (Intel asm convention) cannot be reconstructed.

### MOV RAX, [RAX+const]

This kind of instruction is mostly associated with pointer chasing mystruc = mystruc->next;

This is a significant shortcoming of this approach to capturing memory instruction addresses.

The basic memory access events are shown in the table below:

| _ 1 | 1 1 |   | $\sim$ |

|-----|-----|---|--------|

| a   | h   | Δ | 4      |

| a   | ונו |   | _)     |

| Event Name                                                          | Description Instructions retired which                                                               | umask | Event |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|

| MEM_INST_RETIRED.LOADS                                              | contains a load Instructions retired which                                                           | 01    | 0B    |

| MEM_INST_RETIRED.STORES                                             | contains a store Retired loads that hit the                                                          | 02    |       |

| MEM_LOAD_RETIRED.L1D_HIT                                            | L1 data cache Retired loads that hit the                                                             | 01    | СВ    |

| MEM_LOAD_RETIRED.L2_HIT MEM_LOAD_RETIRED.                           | L2 cache Retired loads that hit the                                                                  | 02    |       |

| LLC_UNSHARED_HIT MEM_LOAD_RETIRED.                                  | LL3 cache Retired loads that hit                                                                     | 04    |       |

| OTHER_CORE_L2_HIT_HITM                                              | sibling core's L2 Retired loads that miss the                                                        | 08    |       |

| MEM_LOAD_RETIRED.LLC _MISS                                          | LL3 cache                                                                                            | 10    |       |

| MEM_LOAD_RETIRED. DROPPED_EVENTS                                    | Retired load info dropped due to data breakpoint Retired loads that miss the L1 data cache and hit a | 20    |       |

| MEM_LOAD_RETIRED.HIT_LFB                                            | line fill buffer Retired loads that miss the                                                         | 40    |       |

| MEM_LOAD_RETIRED.DTLB_MISS                                          | DTLB Memory instructions retired                                                                     | 80    |       |

| MEM_UNCORE_RETIRED.<br>OTHER_CORE_L2_HITM                           | LL3 Cache hit and HITM in sibling core                                                               | 02    | 0F    |

| MEM_UNCORE_RETIRED. REMOTE_CACHE_LOCAL_HOME_HIT MEM_UNCORE_RETIRED. | Memory instructions retired remote cache HIT Memory instructions retired                             | 08    |       |

| REMOTE_DRAM                                                         | remote DRAM Memory instructions retired                                                              | 10    |       |

| MEM_UNCORE_RETIRED.LOCAL_DRAM                                       | local DRAM Memory instructions retired                                                               | 20    |       |

| MEM_UNCORE_RETIRED.UNCACHEABLE                                      | IO Retired stores that miss                                                                          | 80    |       |

| MEM_STORE_RETIRED.DTLB_MISS                                         | the DTLB                                                                                             | 01    | 0C    |

| MEM_STORE_RETIRED. DROPPED_EVENTS                                   | Retired stores dropped due to data breakpoint Retired instructions that                              | 02    |       |

| ITLB_MISS_RETIRED                                                   | missed the ITLB                                                                                      | 20    | C8    |

Strictly speaking the ITLB miss event is really an execution event but is listed here as it is associated with cacheline access.

The precise events listed above allow load driven cache misses to be identified by data source. This does not identify the "home" location of the cachelines with respect to the NUMA configuration. The exceptions to this statement are the events

MEM UNCORE RETIRED.LOCAL DRAM and

MEM\_UNCORE\_RETIRED.NON\_LOCAL\_DRAM. These can be used in conjunction with instrumented malloc invocations to identify the NUMA "home" for the critical contiguous buffers used in an application.

The sum of all the MEM\_LOAD\_RETIRED events will equal the MEM\_INST\_RETIRED.LOADS count.

A count of L1D misses can be achieved with the use of all the MEM\_LOAD\_RETIRED events, except MEM\_LOAD\_RETIRED.L1D\_HIT. It is better to use all of the individual MEM\_LOAD\_RETIRED events to do this, rather than the difference of

MEM\_INST\_RETIRED.LOADS-MEM\_LOAD\_RETIRED.L1D\_HIT because while the total counts of precise events will be correct, and they will correctly identify instructions that caused the event in question, the distribution of the events may not be correct due to PEBS SHADOWING, discussed later in this section.

L1D\_MISSES = MEM\_LOAD\_RETIRED.HIT\_LFB +

MEM\_LOAD\_RETIRED.L2\_HIT + MEM\_LOAD\_RETIRED.LLC\_UNSHARED\_HIT

+ MEM\_LOAD\_RETIRED.OTHER\_CORE\_HIT\_HITM +

MEM\_LOAD\_RETIRED.LLC\_MISS

MEM\_LOAD\_RETIRED.LLC\_UNSHARED\_HIT is not well named. The inclusive L3 CACHE has a bit pattern to identify which core has a copy of the line. If the only bit set is for the requesting core (unshared hit) then the line can be returned from the L3 CACHE with no snooping of the other cores. If multiple bits are set, then the line is in a shared state and the copy in the L3 CACHE is current and can also be returned without snooping the other cores. If the line is read for ownership (RFO) by another core, this will put the copy in the L3 CACHE into an exclusive state. If the line is then modified by that core and later evicted, the written back copy in the L3 CACHE will be in a modified state and snooping will not be required.

MEM\_LOAD\_RETIRED.LLC\_UNSHARED\_HIT counts all of these. The event should really have been called MEM\_LOAD\_RETIRED.LLC\_HIT\_NO\_SNOOP. Similarly, MEM\_LOAD\_RETIRED.LLC\_HIT\_OTHER\_CORE\_HIT\_HITM would have been better named as MEM\_LOAD\_RETIRED.LLC\_HIT\_SNOOP. The author apologizes for this, having been the one responsible for the poor naming.

When a modified line is retrieved from another socket it is also written back to memory. This causes remote HITM access to appear as coming from the home dram. The MEM\_UNCORE\_RETIRED.LOCAL\_DRAM and MEM\_UNCORE\_RETIRED.REMOTE\_DRAM thus also count the L3 CACHE misses satisfied by modified lines in the caches of the remote socket.

There is a difference in the behavior of MEM\_LOAD\_RETIRED.DTLB\_MISSES with respect to that on Intel® Core<sup>TM</sup>2 processors. Previously the event only counted the first miss to the page, as do the imprecise events. The event now counts all loads that result in a miss, thus it includes the secondary misses as well.

## Latency Event

Saving the best for last, the Intel® Core™ i7 processor has a "latency event" which is very similar to the Itanium® Processor Family Data EAR event. This event samples loads, recording the number of cycles between the execution of the instruction and actual deliver of the data. If the measured latency is larger than the minimum latency programmed into MSR 0x3f6, bits 15:0, then the counter is incremented. Counter overflow arms the PEBS mechanism and on the next event satisfying the latency threshold, the measured latency, the virtual or linear address and the data source are copied into 3 additional registers in the PEBS buffer. Because the virtual address is captured into a known location, the sampling driver could also execute a virtual to physical translation and capture the physical address. The physical address identifies the NUMA home location and in principle allows an analysis of the details of the cache occupancies.

Further, as the address is captured before retirement even the pointer chasing encodings MOV RAX, [RAX+const]

have their addresses captured.

Because an MSR is used to program the latency only one minimum latency value can be sampled on a core during a given period. To enable this, the Intel performance tools restrict the programming of this event to counter 4 to simplify the scheduling. The preprogrammed event files used by the Intel® PTU and Vtune<sup>TM</sup> Performance Analyzer contain the following latency events, differing in the minimum latencies required to make them count. Both tools do the required programming of MSR 0x3f6.

| Table 4                                     |                                   |       |       |

|---------------------------------------------|-----------------------------------|-------|-------|

| Event Name                                  | Description                       | umask | Event |

| MEM_INST_RETIRED.LATENCY_ABOVE              | Load instructions retired above 0 |       |       |

| _THRESHOLD_0                                | cycles                            | 10    | 0B    |

| MEM_INST_RETIRED.LATENCY_ABOVE              |                                   |       |       |

| _THRESHOLD_4                                | cycles                            | 10    |       |

| MEM_INST_RETIRED.LATENCY_ABOVE              |                                   |       |       |

| _THRESHOLD_8                                | cycles                            | 10    |       |

| MEM_INST_RETIRED.LATENCY_ABOVE              |                                   | 40    |       |

| _THRESHOLD_10                               | cycles                            | 10    |       |

| MEM_INST_RETIRED.LATENCY_ABOVE              |                                   | 10    |       |

| _THRESHOLD_20                               | cycles                            | 10    |       |

| MEM_INST_RETIRED.LATENCY_ABOVE THRESHOLD 40 |                                   | 10    |       |

| MEM_INST_RETIRED.LATENCY_ABOVE              | cycles                            | 10    |       |

| THRESHOLD 80                                | 128 cycles                        | 10    |       |

| MEM INST RETIRED.LATENCY ABOVE              | •                                 | 10    |       |

| _THRESHOLD_100                              | 256 cycles                        | 10    |       |

| MEM INST RETIRED.LATENCY ABOVE              |                                   | 10    |       |

| WEW_INST_RETIRED.LATENCT_ABOVE              | Load manuchons retired above      | 10    |       |

## Performance Analysis Guide

| _THRESHOLD_200                 | 512 cycles                      |    |

|--------------------------------|---------------------------------|----|

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_400                 | 1024 cycles                     | 10 |

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_800                 | 2048 cycles                     | 10 |

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_1000                | 4096 cycles                     | 10 |

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_2000                | 8192 cycles                     | 10 |

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_4000                | 16384 cycles                    | 10 |

| MEM_INST_RETIRED.LATENCY_ABOVE | Load instructions retired above |    |

| _THRESHOLD_8000                | 32768 cycles                    | 10 |

The Data Source register captured in the PEBS buffer with the Latency Event is interpreted as follows:

| Table 5 Intel® Core™ i7 Processor Data Source Encoding 0x0 0x1 | Data Source short<br>description<br>Unknown Miss<br>L1 Hit | Data Source Longer Description Unknown cache miss. Minimal latency core cache hit. This request was satisfied by the data cache.                                                                              |