# Estrutura de um Computador

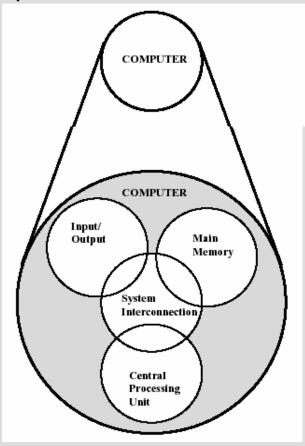

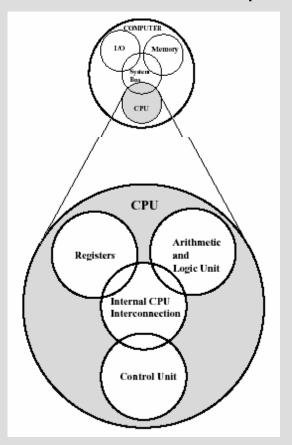

Tratando-se o computador de uma máquina complexa a sua estrutura pode ser apreciada a diferentes níveis de detalhe, duma forma hierárquica.

# Estrutura de um Computador

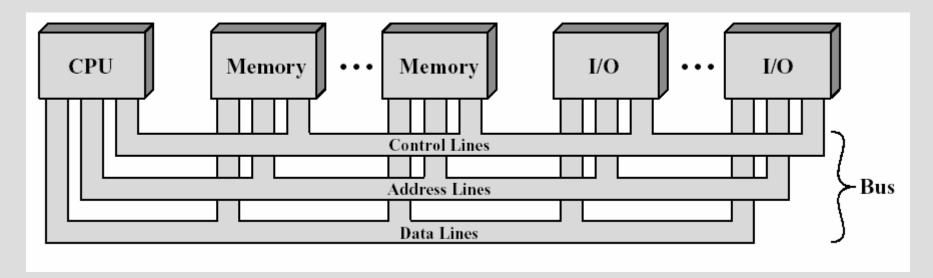

Os diversos componentes do computador comunicam entre si usando um ou mais barramentos.

Os barramentos são constituídos por conjuntos de pistas que conduzem sinais eléctricos, correspondentes a alimentação e sinais lógicos. Estes últimos podem ser classificados em três grupos funcionais distintos:

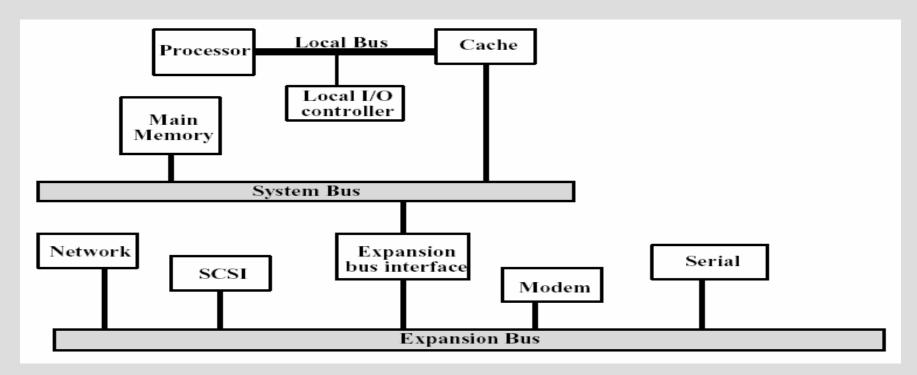

### Hierarquia de Barramentos

Muitos dispositivos ligados ao mesmo barramento = perca de desempenho:

- 1. Barramento mais longo, logo maiores atrasos de propagação de sinal;

- 2. A contenção no barramento aumenta.

**Solução**: hierarquia de barramentos, com diferentes velocidades, e com capacidade para isolarem o tráfego entre si.

#### Memória

A memória está estruturada de forma hierárquica, desde as caches, passando pela memória central até aos discos, CDs, tapes, etc.

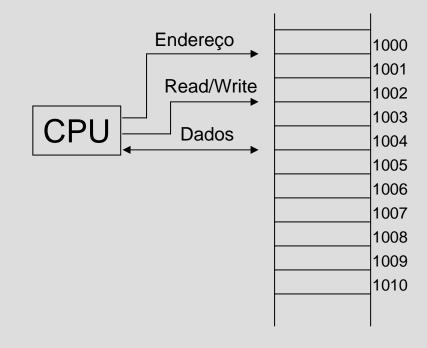

A memória central (RAM) contém dados e programas, sendo acedida pelo processador como se se tratasse de um vector unidimensional.

**Escrita** – CPU envia endereço da posição de memória a ser escrita e dados a escrever.

**Leitura** – CPU envia endereço da posição de memória a ser lida e recebe dados.

### Memória – Estado da Arte

| Label    | Name      | Clock   | Bus      | Bandwidth |

|----------|-----------|---------|----------|-----------|

| PC100    | SDR SDRAM | 100 MHz | 64 bit   | 0,8 GB/s  |

| PC1600   | DDR200    | 100 MHz | 64 bit   | 1,6 GB/s  |

| PC2-1600 | DDR2-200  | 100 MHz | 2*64 bit | 3,2 GB/s  |

| PC3200   | DDR400    | 200 MHz | 64 bit   | 3,2 GB/s  |

| PC2-3200 | DDR2-400  | 200 MHz | 2*64 bit | 6,4 GB/s  |

| PC6400   | DDR800    | 400 MHz | 64 bit   | 6,4 GB/s  |

| PC2-6400 | DDR2-800  | 400 MHz | 2*64 bit | 12,8 GB/s |

| PC2-8520 | DDR2-1066 | 533 MHz | 2*64 bit | 17,1 GB/s |

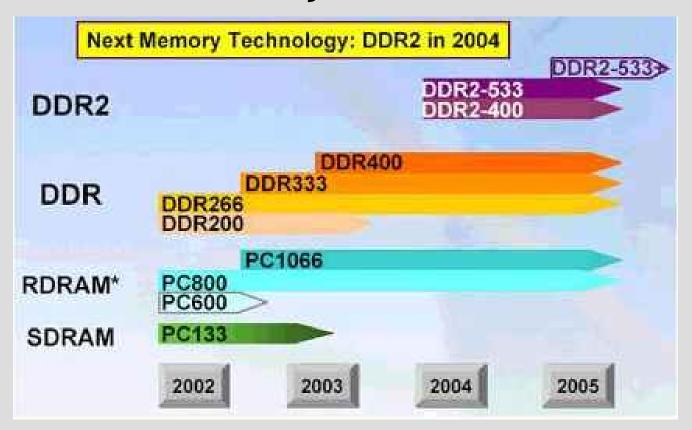

# Memória – Evolução nos últimos anos

Roteiro apresentado pela Intel (Tom's Hardware Guide, Maio 2003)

### **Processadores**

| Nome              | Core | Clock                    | FSB             | HT | L1         | L2            | L3          |

|-------------------|------|--------------------------|-----------------|----|------------|---------------|-------------|

|                   |      |                          |                 |    |            |               |             |

| Pentium 4<br>HT   | 1    | 3.2, 3.4,3.6,<br>3.8 GHz | 800/1066<br>MHz | S  | 16K        | Up to<br>1M   | Up to<br>2M |

| Core 2<br>Extreme | 2    | 2,93 GHz                 | 1066 MHz        |    | 2 x<br>16K | Up to<br>4 MB |             |

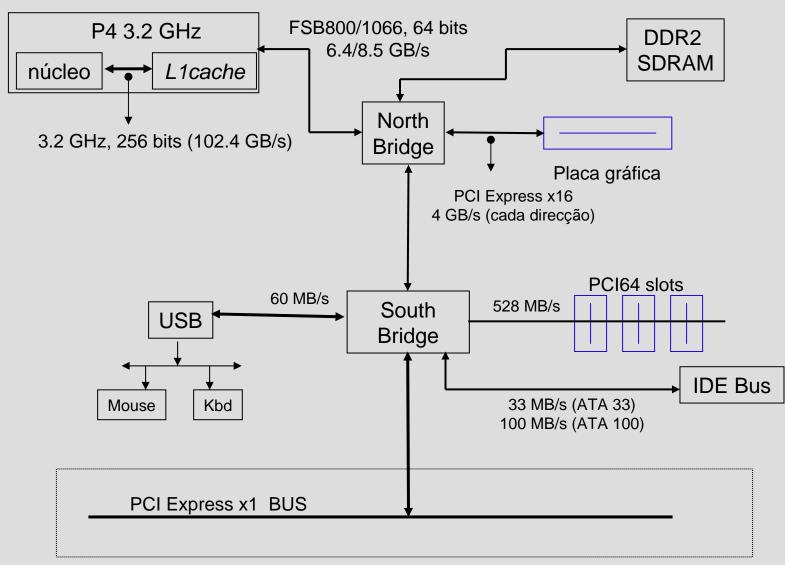

### Estrutura de um PC actual

# Balanceamento dos componentes

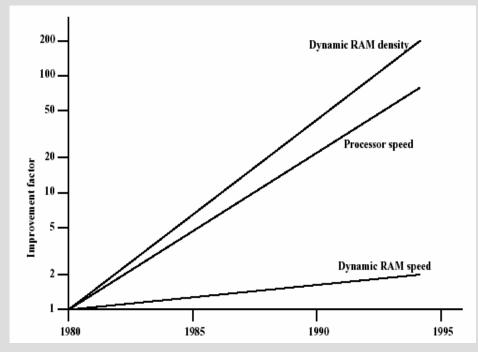

O desempenho da máquina depende do facto de conseguir fornecer dados e instruções aos vários componentes com a mesma frequência com que estes os conseguem processar.

A ligação CPU-memória é a mais crítica, pois se a memória falhar a fornecer dados e instruções à velocidade exigida pelo CPU, este entra em wait state

Problema: o desempenho dos CPUs tem aumentado muito rapidamente, relativamente aos tempos de acesso à DRAM.

#### Balanceamento CPU-memória

Imagine um CPU com uma frequência de 2 GHz, a executar uma instrução por ciclo e com 50% das instruções a exigirem dados da memória. Suponha que tanto as instruções como os dados ocupam 4 bytes cada e que o CPU não tem *cache*.

- 1. Qual a frequência de acesso à memória?

- 2.O barramento visto anteriormente suporta esta frequência?

O processador executa 2\*109 instr/s

Cada instrução são 4 bytes logo, só para código, são 8 GB/s Metade das instruções acedem a dados em memória = 10<sup>9</sup> acessos/s Cada acesso são 4 bytes = 4 GB/s.

No total são 12 GB/s. O barramento anterior suporta 6.4/8.5 GB/s.

**NOTA:** esta configuração é fictícia; os processadores dispõem de cache para diminuir os acessos à memória central.

### Balanceamento dos componentes

- 1. Qual a largura de banda (MB/s) necessária para apresentar um vídeo no monitor, se cada imagem tiver uma resolução de 1024\*768 pontos, cada ponto for especificado por 32 bits e forem apresentadas 30 frames por segundo?

- 2. O computador apresentado no acetato 7 é capaz de apresentar este vídeo, se ele estiver armazenado em memória?

- 3. E se o vídeo estiver armazenado num disco IDE ATA33?

Cada imagem tem 1024\*768 = 786 432 pixels

Cada pixel são 4 bytes logo 786 432 \* 4 = 3 145 738 B/frame Com 30 frames/s temos 3 145 738 \* 30 = 90 MB/s

Se o vídeo estiver em memória pode ser apresentado, pois o PCI Express 16x suporta 4 GB/s.

Se o vídeo estiver num disco IDE ATA33 não pode ser apresentado pois este barramento tem uma largura de banda de 33 MB/s.

### Balanceamento de componentes

- Qual a especificação do barramento PCI (33MHz/32bits, 33MHz/64bits, 66MHz/64 bits) necessária para tirar partido de uma placa de rede de alta velocidade Myrinet, que encaixa neste barramento e transmite dados a 2.0 Gb/s?

- 2. E se o barramento estiver partilhado por outros dispositivos que consumam em média 100 MB/s?

2.0 Gb/s = 2048 Mb/s = 256 MB/s

PCI (33MHz, 32 bits) = 33 \* 4 = 133 MB/s

PCI (33MHz, 64 bits) = 33 \* 8 = 266 MB/s

PCI (66MHz, 64 bits) = 66 \* 8 = 528 MB/s

Se o barramento estiver dedicado para a placa de rede a configuração 33MHz/64bits é suficiente. Com o barramento partilhado o PCI deve ser 66MHz/64 bits

# Sumário

| Tema                          | Hennessy [COD] | Bryant [CS:APP] | Stalling [COA] |

|-------------------------------|----------------|-----------------|----------------|

| Estrutura de um computador    |                |                 | Sec. 1.2       |

| Hierarquia de barramentos     |                |                 | Sec 3.4        |

| Balanceamento dos componentes |                |                 | Sec 2.2        |