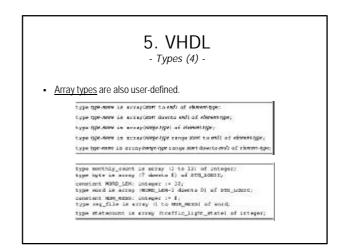

• User-defined types are common in VHDL programs.

Enumerated types are defined by listing the allowed values.

| typo type-manie i.u. ivolae-lati ;                                          | type SCD_BLORIC is (                       |

|-----------------------------------------------------------------------------|--------------------------------------------|

| subtype adopt once is type-news and to end;                                 | 'U', Caunitialised<br>'K', Caccing Takasan |

| supplies against success in the wave main growing end.                      | "i", recoirg 0                             |

| encode week dokeddent.Howe - type Howe online -                             | 'l', Forning 1                             |

|                                                                             | "E', High Impedance                        |

|                                                                             | 'W', Heak Unknown                          |

|                                                                             | "L', Manada D<br>"E', Manada I             |

|                                                                             | tell Barnit annon                          |

|                                                                             | subtype STD LOGIC is resolved STD ULOGIC.  |

|                                                                             |                                            |

|                                                                             |                                            |

| <ul> <li>type traffic_light is (r</li> </ul>                                | eset, stop, start, go);                    |

|                                                                             |                                            |

| <ul><li>type traffic_light is (r</li><li>subtype bitnum is intege</li></ul> |                                            |

|                                                                             | er range 31 downto 0;                      |

### 5. VHDL - Types (5) -

- Array literals can be specified by listing the values in parentheses:

xyz := ('1','1','0','1','1','0','0','1');

abc := (0=>'0', 3=>'0', 9=>'0', others=>'1');

- Strings can be used for STD\_LOGIC arrays: xyz := "11011001"; abc := "0110111110111111";

- Array slices can be specified: xyz(2 to 4) abc(9 downto 0)

- Arrays and array elements can be combined with the concatenation operator (a):

- '0'&'1'&"12" is equivalent to "0112". B(6 downto 0)&B(7) represents a 1-bit left rotate of the B array.

### 5. VHDL

### - Libraries and Packages (1) -

- A library is a place where the VHDL compiler stores information about a particular design project.

- For any design, the compiler creates and uses the work library.

- A design may have multiple files, each containing different units.

- When a file is compiled, the results are placed in the work library.

- Not all information needed in a design must be in the work library. A

designer may rely on common definitions or functions across a family

of different projects.

- A project can refer libraries containing shared definitions: library ieee;

### 5. VHDL

#### - Libraries and Packages (2) -

- Specifying a library gives access to any previously analysed entities and architectures, but does not give access to types and the like.

A <u>package</u> is a file with definitions of objects

- A <u>package</u> is a file with definitions of objects (signals, types, constants, functions, procedures, component declarations) to be used by other programs.

- A design can use a package: use ieee.std\_logic\_1164.all;

- Within the ieee library, the definitions are on file std\_logic\_1164.

nulsaren parlage-roter in tipe derberense ageal dert setser construe derbersten construe derbersten foretten derbersten foretten derbersten ersten der bereiten rotetten bestyrzehenerene im genetiste derbersten foretten derbersten procedure derbersten in Jackage-roter:

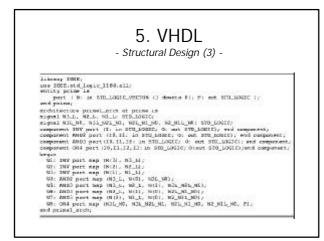

### - Structural Design (1) -

- The body of an architecture is a series of concurrent statements.

- Each concurrent statement executes simultaneously with the other concurrent statements in the same architecture body.

- Concurrent statements are necessary to simulate the behaviour of hardware.

- The most basic concurrent statement is the <u>component statement</u>, betric component some poct map (openFire agent), agent(o); betric component some poct map (port/=signal), port=signal(o); betric component some poct map (port/=signal), port=signal(o);

- component-name is the name of a previously defined entity.

- One instance of the entity is created for each component statement.

### 5. VHDL

- Structural Design (2) -

- Before being instantiated, a component must be declared in the component declaration in the architecture's definition.

- A component declaration is essentially the same as the port declaration part of an entity declaration.

The components used in an architecture may be those previously defined as part of a design, or they may be part of a library.

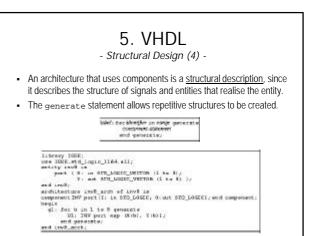

| 5. VHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5. VHDL                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Structural Design (7) -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | - Dataflow Design (1) -                                                                                                                                                                                                                                                                |

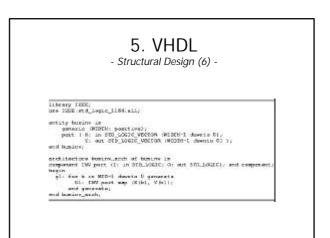

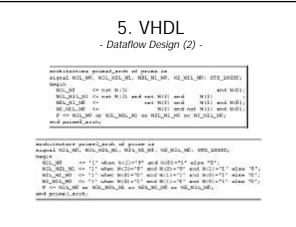

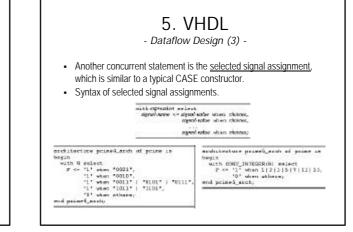

| <pre>iliteory IODE:<br/>use INDER.std_Logic_life.sll;<br/>smithly knows_mergin is<br/>part   1981 is DED_LGGIC_VECTOR (7 downto 0);<br/>OUTE: ext STD_LGGIC_VECTOR (7 downto 0);<br/>OUTE: ext STD_LGGIC_VECTOR (16 downto 0);<br/>OUTE: ext STL_LGGIC_VECTOR (16 downto 0);<br/>OUTE: ext STL_LGGIC_VECTOR (16 downto 0);<br/>OUTE: ext STD_LGGIC_VECTOR (17 downto 0);<br/>OUTE: ext STD_LGGIC_VECTOR (13 downto 0) 1;<br/>OUTE: ext STD_LGGIC_VECTOR (13 downto 0) 1;<br/>OUTE: ext STD_LGGIC_VECTOR (13 downto 0) 1;<br/>OUTE: ext STD_LGGIC_VECTOR (15 downto 0) 1;<br/>O</pre> | <ul> <li>Other concurrent statements allow circuits to be described in terms of the flow of data and operations on it within the circuit.</li> <li>This gives origin to the <u>dataflow description</u> style.</li> <li>Syntax of concurrent signal assignments statements.</li> </ul> |

| <pre>component homine<br/>perceive (MOTY: yesitive);<br/>part 1 %: as STD_LOGIC_VECTOR (#COTM-1 describ 01;<br/>y, and STD_LOGIC_VECTOR (#COTM-1 describ 1);<br/>end companyent;<br/>begin<br/>U: bosine ponecio map (#DFD==4) port map (1000, GOTB);<br/>U: bosine ponecio map (#DFD==4) port map (1000, GOTB);<br/>U: bosine ponecio map (#DFD==4) port map (1000, GOTB);<br/>ui bosine ponecio map (#DFD==4) port map (1000, GOTB);<br/>ui bosine ponecio map (#DFD==4) port map (1010, GOTB);<br/>ui bosine, ponecio map (#DFD==4) port map (1012, GOTB);</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rignel-nexe de optrazion visus booken expression else<br>expression visus booken-expression else<br>expression visus booken-expression else                                                                                                                                            |

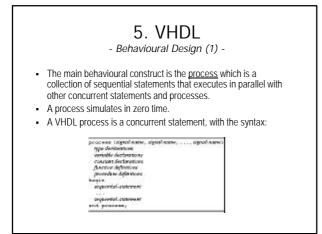

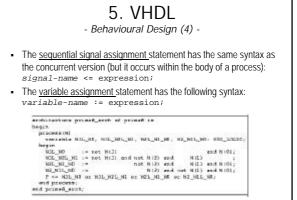

- Behavioural Design (2) -

- A process can not declare signals, only variables, which are used to keep track of the process state.

- The syntax for defining a variable is:

- variable variable-names : variable-type;

- A VHDL process is either running or suspended.

- The list of signals in the process definition (sensitivity list) determines when the process runs.

- A process is initially suspended. When a sensitivity list's signal changes value, the process resumes, starting at the 1st statement until the end.

- If any signal in the sensitivity list change value as a result of running the process, it runs again.

### - Behavioural Design (3) -

- This continues until the process runs without any of these signals changing value.

- In simulation, this happens in zero simulation time.

- Upon resumption, a properly written process will suspend after a couple of runs.

- It is possible to write an incorrect process that never suspends.

- Consider a process with just one sequential statement "x <= not x;" and a sensitivity list of "(x)".

- Since X changes on every pass, the process will run forever in zero simulated time.

- In practice, simulators can detect such behaviour, to end the simulation.

# 5. VHDL Time Dimension (1) None of the previous examples deal with the time dimension of circuit operation: everything happens in zero simulated time. VHDL has excellent facilities for modelling the time. VHDL allows a time delay to be specified by using the keyword after in any signal-assignment statement.

- Z <= '1' after 4ns when X='1' else '0' after 3ns;

- This models a gate that has 4ns of delay on a 0-to-1 output transition and only 3ns on a 1-to-0 transition.

- With these values, a VHDL simulator can predict the approximate timing behaviour of a circuit.

### - Time Dimension (2) -

- Another way to invoke the time dimension is with wait.

- This sequential statement can be used to suspend a process for a specified time period.

- A wait statement can be used to create simulated input waveforms to test the operation of a circuit.

# Which is a substitution of the second secon

### 5. VHDL

### - Simulation (1) -

- Once we have a VHDL program whose syntax and semantics are correct, a simulator can be used to observe its operation.

- Simulator operation begin at simulation time of zero.

- At this time, the simulator initialises all signals to a default value.

- It also initialises any signals and variables for which initial values have been explicitly declared.

- Next, the simulator begins the execution of all processes (and concurrent statements) in the design.

- The simulator uses a time-based event list and a signal-sensitivity matrix to simulate the execution of all the processes.

### 5. VHDL

- At simulation time zero, all processes are scheduled for execution.

- One of them is selected and all of its sequential statements are executed, including any looping behaviour that is specified.

- When the execution of this process is completed, another one is selected, and so on, until all processes have been executed.

- This completes one simulation cycle.

- During its execution, a process may assign new values to signals.

- The new values are not assigned immediately. They are placed on

the event list and scheduled to become effective at a certain time.

### 5. VHDL

- Simulation (3) -

- If the assignment has an explicit simulation time (after clause), then it is scheduled on the event list to occur at that time.

- Otherwise, it is supposed to occur "immediately".

- It is actually scheduled to occur at the current simulation time plus one delta delay.

- The <u>delta delay</u> is an infinitesimally short time, such that the current simulation time plus any number of delta delays still equals the current simulation time.

- The delta delay concept allows processes to execute multiple times (if necessary) in zero simulated time.

- After a simulation cycle completes, the event list is scanned for the signals that change at the next earliest time on the list.

### 5. VHDL

### - Simulation (4) -

- This may be as little as one delta delay, or it may be a real delay, in which case the simulation time is advanced.

- In any case, the scheduled signal changes are made.

- Some processes may be sensitive to the changing signals.

- All the processes that are sensitive to a signal that just changed are scheduled for execution in the next simulation cycle (begins now).

- The simulator's operation goes on indefinitely until the list is empty.The event list mechanism makes it possible to simulate the

- operation of concurrent processes in a uni-processor system.The delta delay mechanism ensures correct operation even though

- a set of processes may require multiple executions.