#### Sistemas Digitais I LESI - 2° ano

#### Lesson 6 - Combinational Design Practices

Prof. João Miguel Fernandes

(miguel@di.uminho.pt)

Dept. Informática

UNIVERSIDADE DO MINHO

- The first PLDs were <u>Programmable Logic Arrays</u> (PLAs).

- A PLA is a combinational, 2-level AND-OR device that can be programmed to realise any sum-of-products logic expression.

- A PLA is limited by:

- the number of inputs (n)

- the number of outputs (m)

- the number of product terms (p)

- We refer to an "n x m PLA with p product terms". Usually,  $p \ll 2^{n}$ .

- An n x m PLA with p product terms contains p 2n-input AND gates and m p-input OR gates.

- Each input is connected to a buffer that produces a true and a complemented version of the signal.

- Potential connections are indicated by Xs.

- The device is programmed by establishing the needed connections.

- The connections are made by fuses.

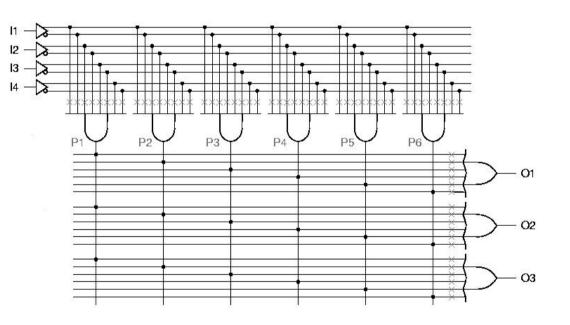

A 4x3 PLA with 6 product terms.

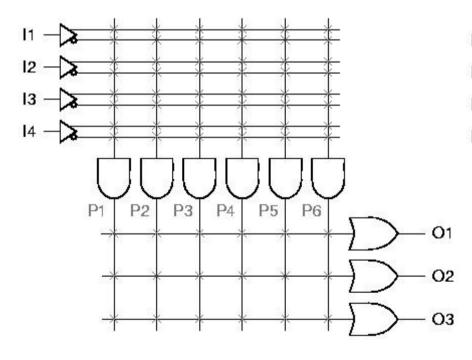

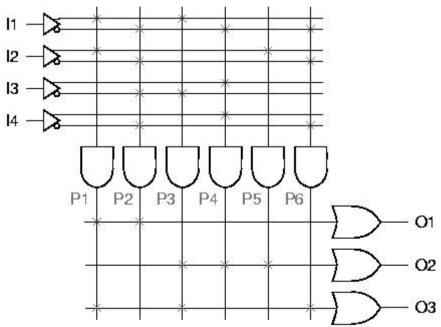

Compact representation of the 4x3 PLA with 6 product terms.

•  $O1 = |1 \cdot |2 + |1' \cdot |2' \cdot |3' \cdot |4'$   $O2 = |1 \cdot |3' + |1' \cdot |3 \cdot |4 + |2$  $O3 = |1 \cdot |2 + |1 \cdot |3' + |1' \cdot |2' \cdot |4'$

- Another PLD is PAL (Programmable Array Logic).

- A PAL device has a fixed OR array.

- In a PAL, product terms are not shared by the outputs.

- A PAL is usually faster than a similar PLA.

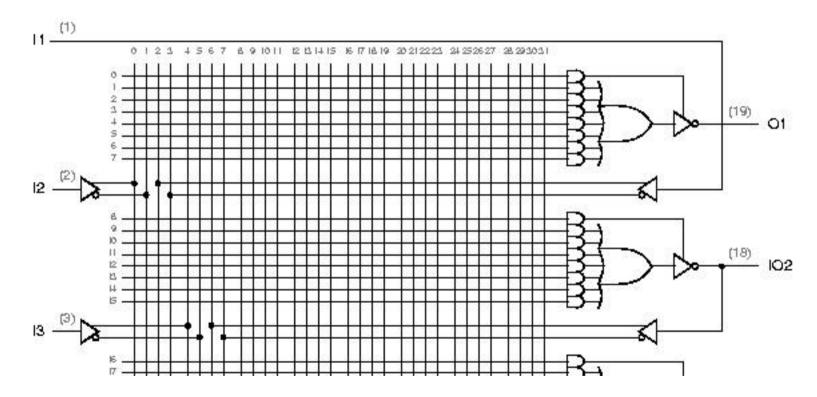

• Part of the logic diagram of the PAL 16L8.

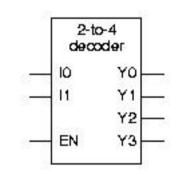

#### 6. Combinational Practices - Decoders (1) -

- A decoder is a circuit that converts coded inputs into coded outputs.

- Usually, the input code has fewer bits than the output code.

- The most common decoder is an n-to-2<sup>n</sup> or binary decoder.

- A binary decoder is used when one of 2<sup>n</sup> outputs needs to be activated based on an n-bit input value.

| inputs |    |    | Outputs |    |    |    |  |

|--------|----|----|---------|----|----|----|--|

| EN     | 11 | 10 | YЭ      | ¥2 | ΥI | YO |  |

| 0      | x  | x  | 0       | 0  | 0  | 0  |  |

| 1      | 0  | o  | 0       | 0  | 0  | 1  |  |

| 1      | 0  | 1  | 0       | 0  | 1  | 0  |  |

| 1      | 1  | 0  | 0       | 1  | 0  | 0  |  |

| 1      | 1  | 1  | 1       | 0  | 0  | 0  |  |

#### 6. Combinational Practices - Decoders (2) -

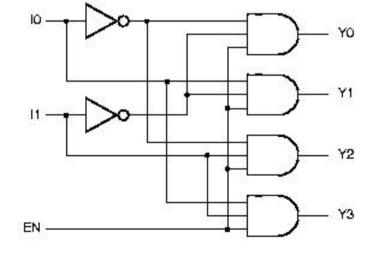

• A 74x139 IC has two independent 2-to-4 decoders.

| ín  | puls |   | Outputs |      |      |      |  |

|-----|------|---|---------|------|------|------|--|

| G_L | в    | A | ¥9_L    | ¥2_L | ¥1_L | YO_L |  |

| 1   | x    | x | 1       | 1    | 1    | 1    |  |

| 0   | 0    | 0 | 1       | 1    | 1    | 0    |  |

| 0   | 0    | 1 | 1       | 1    | o    | 1    |  |

| 0   | 1    | 0 | 1       | 0    | 1    | 1    |  |

| 0   | 1    | 1 | 0       | 1    | 1    | 1    |  |

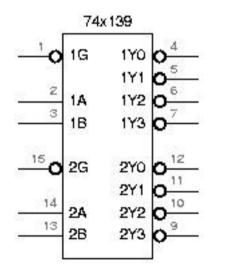

#### 6. Combinational Practices - Decoders (3) -

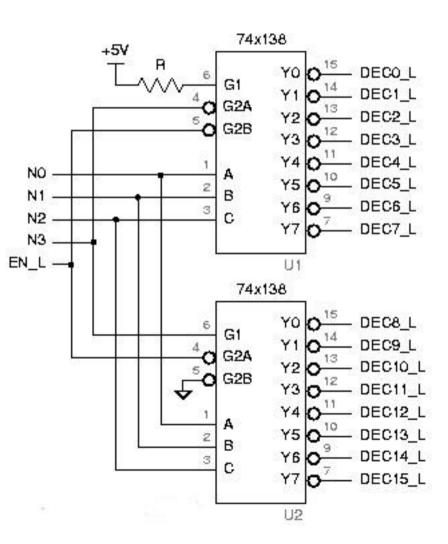

A 74x138 IC has one 3-to-8 decoder.

- Multiple decoders can be used to decode larger code words.

- The top decoder (U1) is enabled when N3 is 0, and the bottom decoder (U2) is enabled when N3 is 1.

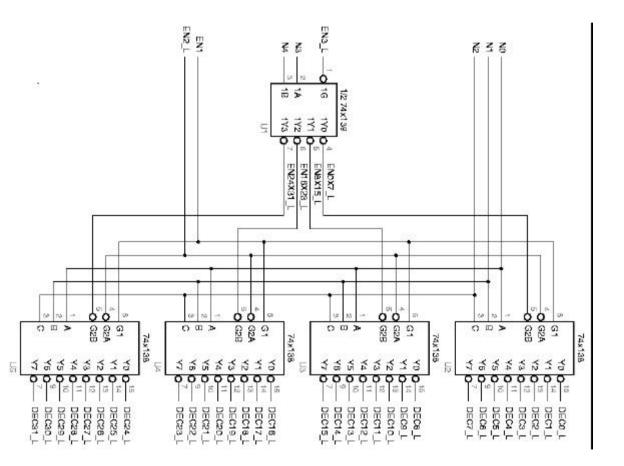

- To handle larger code words, decoders can be cascaded hierarchically.

- To handle larger code words, decoders can be cascaded hierarchically.

- A 5-to-32 decoder can be built with one 2-to-4 and four 3-to-8 decoders.

- The 2-to-4 decoder treats the high order bits.

- The 3-to-8 decoders treat the low-order bits.

#### 6. Combinational Practices - Decoders (6) -

- There are several ways to write decoders in VHDL.

- The most primitive would be to write a structural description equivalent to the logic circuit on slide 7.

```

library IEEE;

use IEEE.std logic 1164.all;

entity V2to4dec is

port (IO, I1, EN: in STD LOGIC;

Y0, Y1, Y2, Y3: out STD LOGIC );

end V2to4dec;

Architecture V2to4dec s of V2to4dec is

signal NOTIO, NOTI1: STD LOGIC;

component inv port (I: in STD_LOGIC; O: out STD_LOGIC ); end component;

component And3 port (I0, I1, I2: in STD LOGIC; O: out STD LOGIC ); end component;

begin

U1: inv port map (10,NOTIO);

U2: inv port map (I1, NOTI1);

U3: and3 port map (NOTI0, NOTI1, EN, Y0);

U4: and3 port map ( I0,NOTI1,EN,Y1);

US: And3 port map (NOTIO, 11, EN, Y2);

U6: and3 port map ( I0, I1, EN, Y3);

end V2to4dec s;

```

#### 6. Combinational Practices - Decoders (7) -

The second alternative is using the dataflow style.

```

library IEEE;

use IEEE.std logic 1164.all;

entity V74x138 is

port (G1, G2A_L, G2B_L: in STD_LOGIC; -- enable inputs

A: in STD LOGIC VECTOR (2 downto 0); -- select inputs

Y L: out STD LOGIC VECTOR (0 to 7) ); -- decoded outputs

end V74x138;

Architecture V74x138 & of V74x138 is

signal Y_L_i: STD_LOGIC_VECTOR (0 to 7);

begin

with A select Y_L_i <=

"011111111" when "000",

"101111111" when "001".

"110111111" when "010",

"111011111" when "011",

"11110111" when "100",

"11111011" when "101",

"111111101" when "110".

"111111110" when "111",

"111111111" when others;

Y_L <= Y_L_i when (G1 and not G2A_L and not G2B_L)='1' else "11111111";

end V74x138_a;

```

#### 6. Combinational Practices - Decoders (8) -

Another alternative is using the behavioral style.

```

architecture V3to8dec_c of V3to8dec is

begin

process (G1, G2, G3, A)

variable i: INTEGER range 0 to 7;

begin

Y <= "00000000";

if (G1 and G2 and G3) = '1' then

for i in 0 to 7 loop

if i=CONV_INTEGER(A) then Y(i) <= '1'; end if;

end loop;

end if;

end process;

end V3to8dec_c;

```

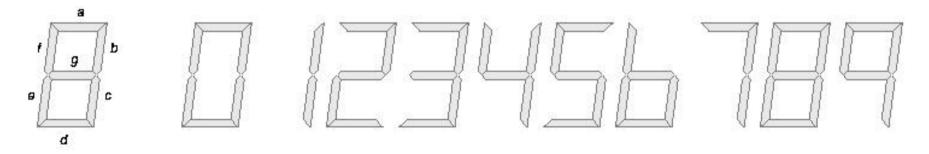

#### 6. Combinational Practices - 7-Segment Decoders (1) -

- A <u>7-segment display</u> is used in watches, calculators, and devices to show decimal data.

- A digit is displayed by illuminating a subset of the 7 line segments.

• A <u>7-segment decoder</u> has a 4-bit BCD as its input and the 7-segment code as its output.

#### 6. Combinational Practices - 7-Segment Decoders (2) -

|      | ínputs |   |   |   |   | Outputs |   |   |   |   |   |

|------|--------|---|---|---|---|---------|---|---|---|---|---|

| BI_L | D      | С | в | А | а | ь       | c | d | e | f | 9 |

| 0    | x      | x | x | x | 0 | 0       | 0 | 0 | 0 | 0 | 0 |

| 1    | 0      | 0 | 0 | 0 | 1 | 1       | 1 | 1 | 1 | 1 | 0 |

| 1    | о      | 0 | o | 1 | o | 1       | 1 | 0 | о | o | 0 |

| 1    | 0      | 0 | 1 | 0 | 1 | 1       | 0 | 1 | 1 | 0 | 1 |

| 1    | 0      | 0 | 1 | 1 | 1 | 1       | 1 | 1 | 0 | 0 | 1 |

| 1    | o      | 1 | o | 0 | o | 1       | 1 | 0 | o | 1 | 1 |

| 1    | 0      | 1 | 0 | 1 | 1 | 0       | 1 | 1 | 0 | 1 | 1 |

| 1    | 0      | 1 | 1 | 0 | 0 | 0       | 1 | 1 | 1 | 1 | 1 |

| 1    | o      | 1 | 1 | 1 | 1 | 1       | 1 | 0 | o | o | 0 |

| 1    | 1      | 0 | 0 | 0 | 1 | 1       | 1 | 1 | 1 | 1 | 1 |

| 1    | 1      | o | 0 | 1 | 1 | 1       | 1 | 0 | 0 | 1 | 1 |

| 1    | 1      | o | 1 | o | o | o       | 0 | 1 | 1 | 0 | 1 |

| 1    | 1      | 0 | 1 | 1 | 0 | 0       | 1 | 1 | 0 | 0 | 1 |

| 1    | 1      | 1 | 0 | 0 | 0 | 1       | 0 | 0 | 0 | 1 | 1 |

| 1    | 1      | 1 | 0 | 1 | 1 | 0       | 0 | 1 | 0 | 1 | 1 |

| 1    | 1      | 1 | 1 | 0 | 0 | 0       | 0 | 1 | 1 | 1 | 1 |

| 1    | 1      | 1 | 1 | 1 | o | 0       | 0 | o | o | 0 | 0 |

- Exercise 1: Obtain minimised expressions for outputs of the 7segment decoder.

- Exercise 2: Write a VHDL description of a 7segment decoder.

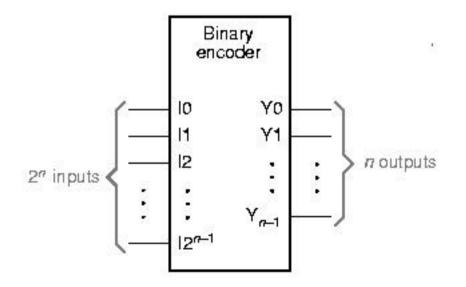

#### 6. Combinational Practices - Encoders (1) -

- An <u>encoder</u> is a circuit whose output code has normally fewer bits than its input code.

- The simplest encoder to build is a 2<sup>n</sup>-to-n or binary encoder. It has the opposite function as a binary encoder.

- Equations for an 8-to-3 encoder : Y0 = I1 + I3 + I5 + I7 Y1 = I2 + I3 + I6 + I7 Y2 = I4 + I5 + I6 + I7

- Only 1 input is active at a time.

What happens if 2 inputs are asserted (ex: I2 and I4)?

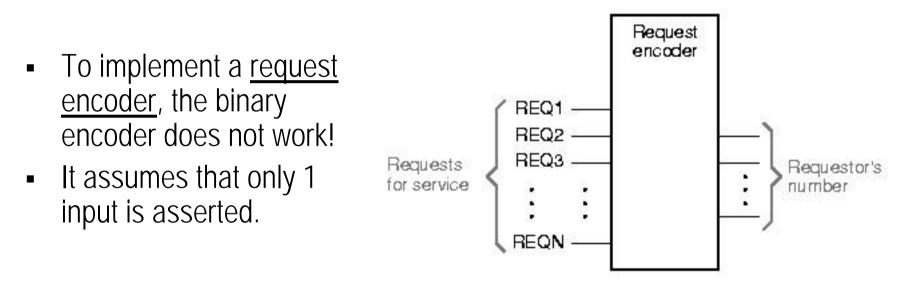

#### 6. Combinational Practices - Encoders (2) -

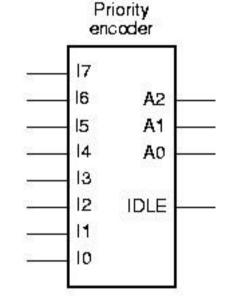

- If multiple requests can be made simultaneously, a <u>priority</u> must be assigned to the input lines.

- When multiple requests are made, the device (priority encoder) produces the number of the highest-priority requestor.

- Input I7 has the highest priority.

- Outputs A2-A0 contain the number of the highest-priority asserted input, if any.

- The IDLE output is asserted if no inputs are asserted.

- Intermediate variable Hi is 1, if Ii is the highest priority 1-input: H7 = I7 H6 = I6·I7' H5 = I5·I6'·I7' H4 = I4·I5'·I6'·I7' ... (similar equations for H3-H0)

- A0 = H1 + H3 + H5 + H7

A1 = H2 + H3 + H6 + H7

A2 = H4 + H5 + H6 + H7

- IDLE= 10'·11'·12'·13'·14'·15'·16'·17'

#### 6. Combinational Practices - Multiplexers (1) -

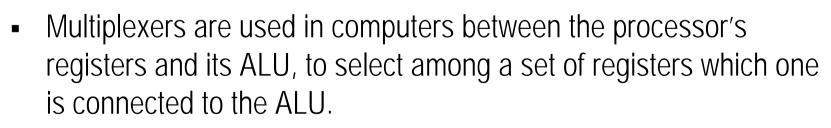

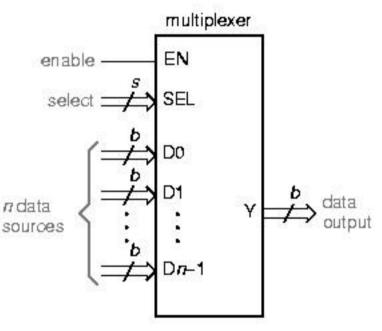

- A <u>multiplexer</u> (mux) is a digital switch.

- It connects data from one of n sources to its output.

- The SEL input selects among the n sources, so s = [log<sub>2</sub> n].

- When EN=0, Y=0;

When EN=1, the mux is working.

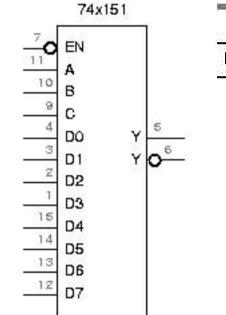

- A 74x151 IC has one 8input, 1-bit multiplexer.

- The select inputs are named A,B,C, where C is the MSB.

- The enable input EN\_L is active low.

- Both active-low and high versions of the output are provided

|      | Inpi | Oa | tputs 🛛 |    |     |

|------|------|----|---------|----|-----|

| EN_L | C    | В  | A       | Ŷ  | Y_L |

| 1    | X    | ×  | ×       | 0  | 1   |

| 0    | 0    | 0  | 0       | D0 | D0' |

| 0    | 0    | 0  | 1       | D1 | D1' |

| 0    | 0    | 1  | 0       | D2 | D2′ |

| 0    | 0    | 1  | ÷.      | D3 | D3' |

| 0    | 10   | 0  | 0       | D4 | D4' |

| 0    | 10   | 0  | 1       | DS | D5' |

| 0    | 1    | 1  | 0       | D6 | D6' |

| 0    | 1    | 1  | 1       | D7 | D7' |

- Multiplexers (3) -

- A 74x157 IC has one 2-input, 4-bit multiplexer.

- The select input is S.

- The enable input G\_L is active low.

- The truth table was extended and inputs appear at the outputs columns.

| Inputs            |     | Outputs |    |    |    |  |

|-------------------|-----|---------|----|----|----|--|

| G_L               | S   | 14      | 2Y | ЗY | 4Y |  |

| 1                 | X   | 0       | 0  | 0  | 0  |  |

| 0                 | 0   | 1A      | 2A | ЗA | 4A |  |

| 0                 | 1   | 16      | 28 | 36 | 46 |  |

| and in the second | 100 |         |    |    |    |  |

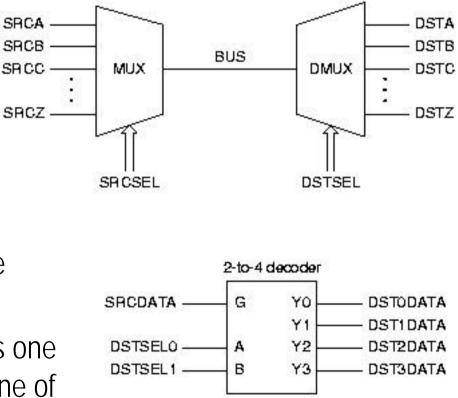

- A multiplexer can be used to select one of n sources of data to transmit on a bus.

- At the other end, a demultiplexer can be used to route the bus to one of m destinations.

- The function of a multiplexer is the inverse of a demultiplexer's.

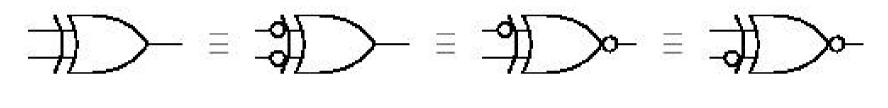

- A 1-bit, n-output demultiplexer has one data input and s inputs to select one of the n=2<sup>s</sup> data outputs.

#### 6. Combinational Practices - Multiplexers (5) -

- It is easy to describe multiplexers in VHDL.

- In the dataflow style, a SELECT statement is required.

```

library IEEE;

use IEEE. std_logic_1104.all;

entity mux4inBb is

port (

S: in STD_LOGIC_VECTOR (1 downto 0);

-- Select imputs, 0-3 ==> A-D

A, B, C, D: in STD_LOGIC_VECTOR (1 to B); -- Data bus input

Y: out STD_LOGIC_VECTOR (1 to B)

-- Data bus output

33.

and mussings;

architecture mundiage of mundiage is

begin

with 5 select Y <=

A when "00",

B when "OI".

C when "10",

D when "II".

(others =: 'U') when others: -- this creates an B-bit vector of 'U'

and mussings;

```

#### 6. Combinational Practices - Multiplexers (6) -

• In a behavioural architecture, a CASE statement is used.

```

architecture mux&inEp of mux&inEb is

begin

process(S, A, B, C, D)

begin

case 5 is

when *00* => Y <= A;

when *01* => Y <= B;

when *10* => Y <= C;

when *10* => Y <= D;

when others => Y <= (others => 'U'); -- B-bit vector of 'U'

end case;

end process;

end mux&inEp;

```

It is easy to customise the selection criteria in a VHDL multiplexer program.

- XOR and Parity Circuits (1) -

- An <u>Exclusive-OR (XOR)</u> gate is a 2-input gate whose output is 1, if exactly one of its inputs is 1.

- An XOR gate produces a 1 output if its input are different.

| x            | Y | X⊕ Y<br>(XOR) | (X⊕Y)<br>(XNOR) |  |

|--------------|---|---------------|-----------------|--|

| 0            | 0 | 0             | 1               |  |

| 0            | 1 | 1             | 0               |  |

| S <b>1</b> 8 | 0 | 12            | . <b>O</b>      |  |

| <b>1</b>     | 1 | 0             | <b>1</b>        |  |

- An <u>Exclusive-NOR (XNOR)</u> is just the opposite: it produces a 1 output if its inputs are the same.

- The XOR operation is denoted by the symbol  $\oplus$ .

- $X \bigoplus Y = X' \cdot Y + X \cdot Y'$

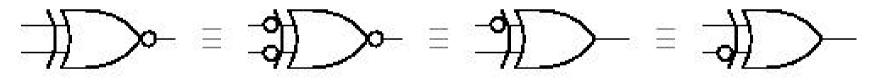

• There are 4 symbols for each XOR and XNOR function.

- These alternatives are a consequence of the following rule:

- Any two signals (inputs or output) of an XOR or XNOR gate may be complemented without changing the resulting logic function.

- In bubble-to-bubble design we choose the symbol that is most expressive of the logic function being performed.

- XOR and Parity Circuits (3) -

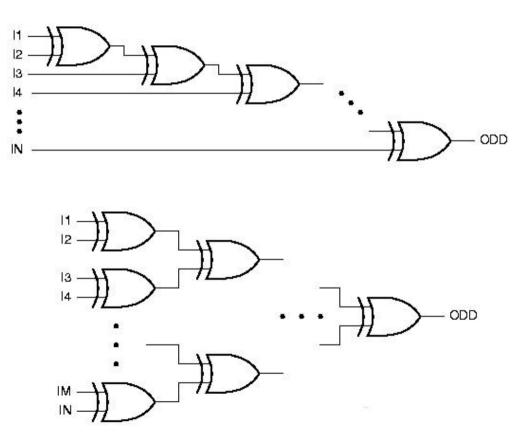

- n XOR gates may be cascaded to form a circuit with n+1 inputs and a single output. This is a <u>odd-parity circuit</u>, because its output is 1 if an odd number of its inputs are 1.

- If the output of either circuit is inverted, we get an even-parity circuit, whose output is 1 if an even number of its inputs are 1.

- XOR and Parity Circuits (4) -

- VHDL provides the primitive operators xor and xnor.

- A 3-input XOR device can be specified in VHDL dataflow style program.

```

library IEEE;

use IEEE.std_logic_1104.all;

entity vmor3 is

port (A, B, C: in STD_LOGIC)

Y: out STD_LOGIC);

end vmor3;

architecture vmor3 of vmor3 is

begin

Y <= A mor B mor C;

end vmor3;

```

- XOR and Parity Circuits (5) -

A 9-input parity function can be specified behaviourally.

```

library IEEE;

use IEEE.std_logic_1104.all;

entity parity9 is

port (I: in STD_LOGIC_VECTOR (1 to 9);

EVEN, CDD: out STD_LOGIC);

end parity9;

architecture parity9p of parity9 is

begin

process (I)

variable p : STD_LOGIC;

Ърділ

p := I(1);

for j in Z to 9 loop

if I(j) = ii then p := not p; and if;

end loop;

ODD <= p;

EVEN <= not p;

and process;

end parity9p;

```

- Comparing two binary words is a common operation in computers.

- A circuit that compares 2 binary words and indicates whether they are equal is a <u>comparator</u>.

- Some comparators interpret their input as signed or unsigned numbers and also indicate an arithmetic relationship (greater or less than) between the words.

- These circuits are often called <u>magnitude comparators</u>.

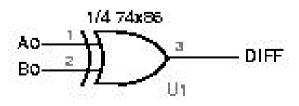

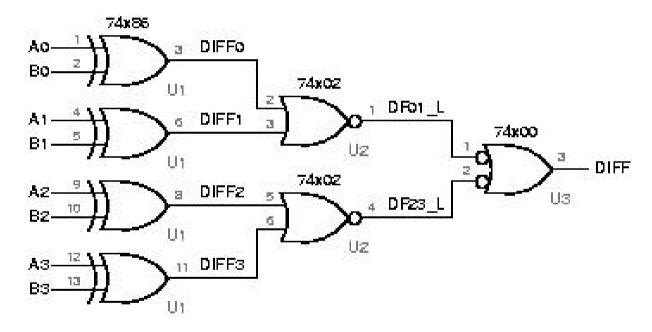

- XOR and XNOR gates can be viewed as 1-bit comparators.

- The DIFF output is asserted if the inputs are different.

• The outputs of 4 XOR gates can be ORed to create a 4-bit comparator.

- The DIFF output is asserted if any of the input-bit pairs are different.

- This circuit can be easily adapted to any number of bits per word.

#### 6. Combinational Practices - Comparators (3) -

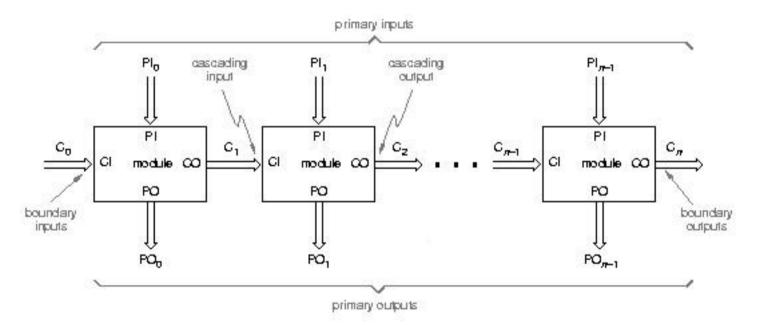

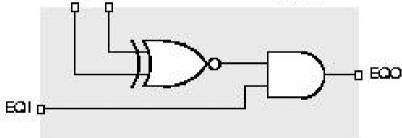

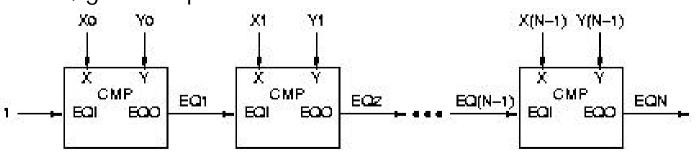

• An <u>iterative circuit</u> is a combinational circuit with the following structure.

- The circuit contains n identical modules, each of which has <u>both primary</u> <u>inputs and outputs</u> and <u>cascading inputs and outputs</u>.

- The left-most cascading inputs are usually connected to fixed values.

#### 6. Combinational Practices - Comparators (4) -

- Two n-bit values X and Y can be compared one bit at a time using a single bit EQ<sub>i</sub> at each step to keep track of whether all of the bit-pairs have been equal so far:

- 1. Set EQ<sub>0</sub> to 1 and set *i* to 0.

2. If EQ<sub>i</sub> is 1 and X<sub>i</sub>=Y<sub>i</sub>, set EQ<sub>i+1</sub> to 1. Else set EQ<sub>i+1</sub> to 0.

- 3. Increment *i*.

CMP.

4. If *i* < *n*, go to step 2.

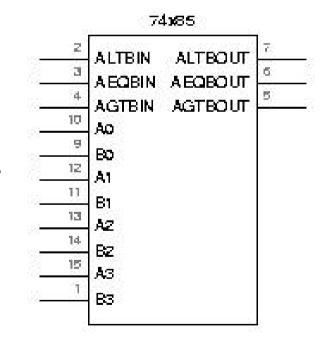

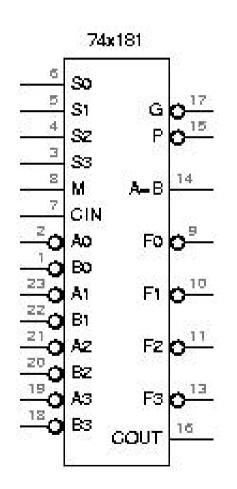

- Several MSI comparators have been developed commercially.

- The 74x85 is a 4-bit comparator.

- It provides a greater-than output, a less-than output and an equal output.

- The 74x85 also has cascading inputs for combining multiple chips to create comparators for more than 4 bits.

- AGTBOUT =  $(A>B) + (A=B) \cdot AGTBIN$ AEQBOUT =  $(A=B) \cdot AEQBIN$ ALTBOUT =  $(A<B) + (A=B) \cdot ALTBIN$

#### 6. Combinational Practices - Comparators (6) -

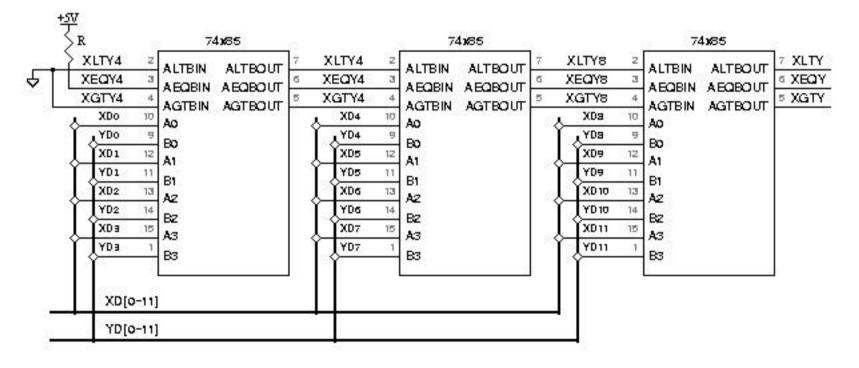

• With three 74x85 circuits, a 12-bit comparator can be built.

- VHDL has comparison operators for all of its built-in types.

- Equality (=) and inequality (/=) operators apply to all types.

- For array and record types, the operands must have equal size and structure, and the operands are compared component by component.

- VHDL's other comparison operators (>, <, >=, <=) apply only to integers, enumerated types and one-dimensional arrays of enumeration or integer types.

- Adders, Subtractors and ALUs (1) -

- Addition is the most commonly performed arithmetic operation in digital systems.

- An <u>adder</u> combines two arithmetic operands using the addition rules.

- The same addition rules, and hence the same adders, are used for both unsigned and 2's complement numbers.

- An adder can perform subtraction as the addition of the minuend and the complemented subtrahend.

- A <u>subtractor</u> can also be built to perform subtraction directly.

- An <u>ALU</u> (Arithmetic and Logic Unit) performs addition, subtraction, and other logical operations.

- Adders, Subtractors and ALUs (2) -

- The simplest adder, called a <u>half adder</u>, adds two 1-bit operands X and Y, producing a 2-bit sum.

- The sum can range from 0 to 2, which requires two bits to express.

- The low-order bit of the sum may be named HS (half sum).

- The high-order bit of the sum may be named CO (carry out).

- The following equations can be written:

HS = X ⊕ Y = X · Y' + X' · Y

CO = X · Y

- To add operands with more than one bit, carries between bit positions must be provided.

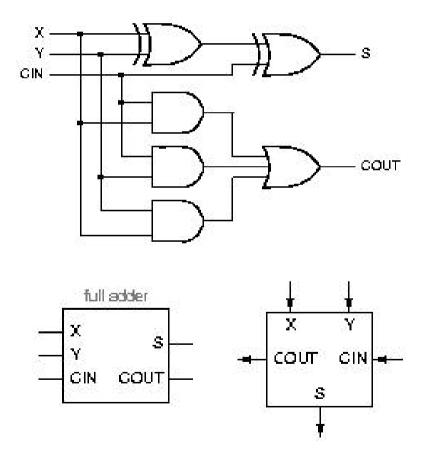

- Adders, Subtractors and ALUs (3) -

- The building block for this operation is called a <u>full adder</u>.

- Besides the addend-bit inputs X and Y, a full adder has a <u>carry-bit input</u>, CIN.

- The sum of the 3 bits can range from 0 to 3, which can still be expressed with just two output bits, S and COUT.

- The following equations can be written:

S = X ⊕ Y ⊕ CIN

COUT = X·Y + X·CIN + Y·CIN

- Adders, Subtractors and ALUs (4) -

- Two binary words, each with n bits, can be added using a ripple adder.

- A <u>ripple adder</u> is a cascade of n full-adders stages, each of which handles one bit.

- The carry input to the least significant bit  $(c_0)$  is usually set to 0.

- The carry output of each full adder is connected to the carry input of the next most significant full adder.

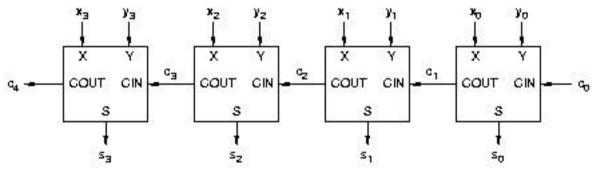

- Adders, Subtractors and ALUs (5) -

- The binary subtraction operation is analogous to binary addition.

- A <u>full subtractor</u> has inputs X (minuend), Y (subtrahend) and BIN (borrow in) and outputs D (difference) and BOUT (borrow out).

- The following equations can be written:

$D = X \bigoplus Y \bigoplus BIN$  $BOUT = X' \cdot Y + X' \cdot BIN + Y \cdot BIN$

- These equations are similar to the equations for a full adder.

D = X ⊕ Y' ⊕ BIN'

BOUT = X·Y' + X·BIN' + Y'·BIN'

- A full subtractor can be built from a full adder. X-Y = X+Y'+1

- Adders, Subtractors and ALUs (6) -

- Adders, Subtractors and ALUs (7) -

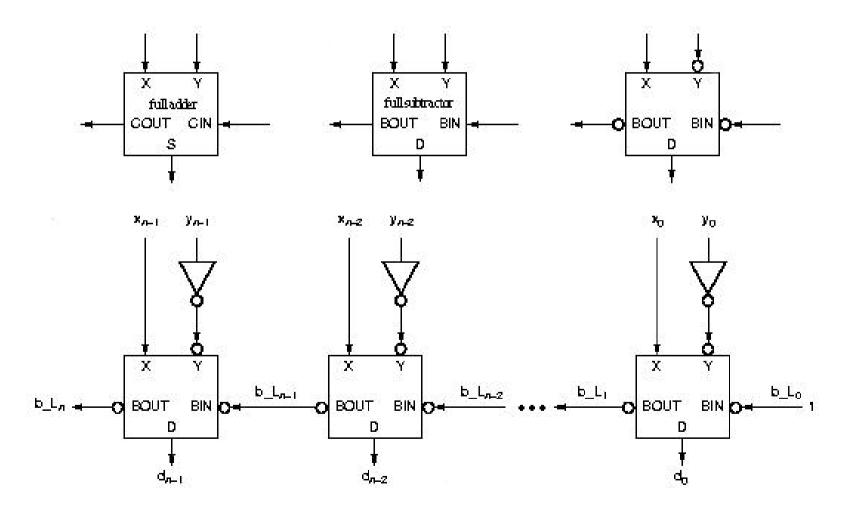

- An <u>ALU</u> is a combinational circuit that can perform several arithmetic and logical operations on a pair of b-bit operands.

- The operation to be performed is specified by a set of function-select inputs.

- Typical MSI ALUs have 4-bit operands and three to five function-select inputs, allowing up to 32 different functions to be performed.

- A 74x181 IC has one 4-bit ALU.

- The operation performed by the 74x181 is selected by the M and S3-S0 inputs.

- Adders, Subtractors and ALUs (8) -

| top ats |           |               |             | Function                                   |                                            |

|---------|-----------|---------------|-------------|--------------------------------------------|--------------------------------------------|

| S3      | S2        | S1            | <b>S</b> 0  | M=0 (arithmetic)                           | .M = 1 (logic)                             |

| 0       | 0         | 30.0          | 0           | F= A minus 1 plus CIN                      | F = A'                                     |

| 0       | 0         | 3 <b>9</b> 3  | <u>_1</u>   | F = A · B minus 1 plus CIN                 | F = A' + B'                                |

| 0       | 0         | 1             | 0           | F= A · B' minus 1 plusCIN                  | F = A' + B                                 |

| 0       | 0         | 1             | 1           | F= 1111 plus CIN                           | F = 1111                                   |

| 0       | 1         | 0             | 0           | F = A plus (A + B') plus CIN               | $F=A'\cdot B'$                             |

| 0       | 1         | 0             | 1           | $F = A \cdot B p lus (A + B') p lus CIN$   | F = 8'                                     |

| 0       | 1         | 1             | 0           | F= A minus B minus 1 plus CIN              | F = A 🕀 B'                                 |

| 00      | 1         | 18            | 39 <b>1</b> | F= A + B' plus CIN                         | F = A + B'                                 |

| 1       | 0         | 30 <b>0</b> 3 | 0           | F = A plus(A + B) plus CIN                 | $F=A'\cdotB$                               |

| 1       | 0         | <u>0</u>      | 1           | F= A plus B plus CIN                       | F = A ⊕ B                                  |

| 1       | 0         | 1             | 0           | $F = A \cdot B'$ plus ( $A + B$ ) plus CIN | F = B                                      |

| 1       | ø         | 1             | 1           | F= A + B plus CIN                          | F = A + B                                  |

| 1       | 1         | 0             | Q           | F= A plus A plus CIN                       | F=0000                                     |

| 1       | i.        | Q             | 1           | F= A · B plus A plus CIN                   | $F=A\cdotB'$                               |

| 1       | 1         | 1             | 0           | F = A ⋅ B′ plus A plus CIN                 | $\mathbf{F} = \mathbf{A} \cdot \mathbf{B}$ |

| 1       | <u>:1</u> | 13            | 9: <b>1</b> | F= A plus CIN                              | E = A                                      |

- Adders, Subtractors and ALUs (9) -

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity vaddshr is

port (

A, B, C, D: in SIGNED (7 downto 0);

SEL: in STD_LOGIC;

S: out SIGNED (7 downto 0)

);

end vaddshr;

architecture vaddshr_arch of vaddshr is

begin

S <= A + B when SEL = '1' else C + D;

end vaddshr_arch;

```

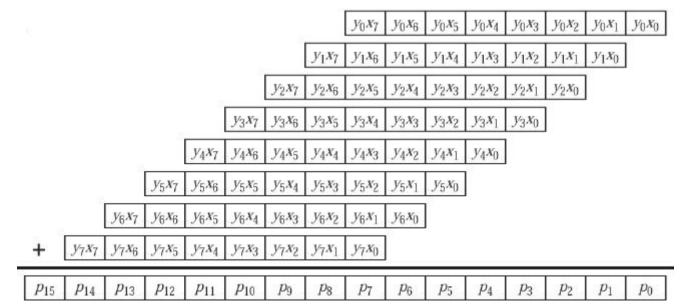

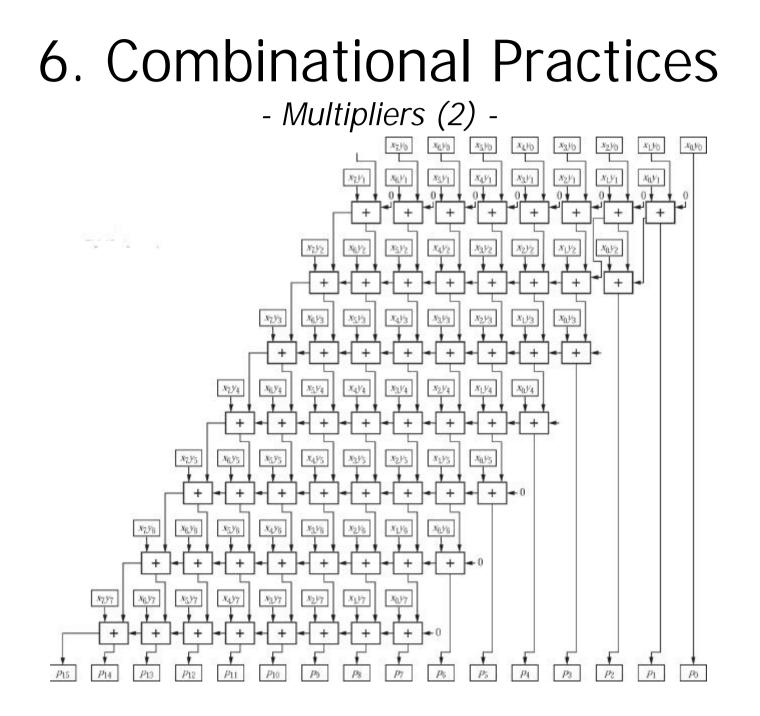

- Multipliers (1) -

- The traditional algorithm to multiply binary numbers uses shifts and adds to obtain the result.

- However, it is not the only solution to implement a multiplier.

- Given 2 n-bit inputs (X, Y), we can write a truth table that expresses the 2n-bit product P=X×Y as a combinational function of X and Y.

- Most approaches to combinational multipliers are based on the traditional shift-and-add algorithm.

#### 6. Combinational Practices - Multipliers (3) -

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

entity vmul8x8i is

port (

X: in UNSIGNED (7 downto 0);

Y: in UNSIGNED (7 downto 0);

P: out UNSIGNED (15 downto 0)

);

end vmul8x8i;

architecture vmul8x8i_arch of vmul8x8i is

begin

P <= X * Y;

end vmul8x8i_arch;

```