# Intel<sup>®</sup> oneAPI Programming Guide (Beta)

Copyright © 2019 Intel Corporation All Rights Reserved

## **Notices and Disclaimers**

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at [intel.com].

The products and services described may contain defects or errors which may cause deviations from published specifications. Current characterized errata are available on request. Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel, the Intel logo, Intel Atom, Intel Arria, Intel Core, VTune and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

Microsoft, Windows, and the Windows logo are trademarks, or registered trademarks of Microsoft Corporation in the United States and/or other countries.

OpenCL and the OpenCL logo are trademarks of Apple Inc. used by permission of The Khronos Group.

\*Other names and brands may be claimed as the property of others.

#### © Intel Corporation.

This software and the related documents are Intel copyrighted materials, and your use of them is governed by the express license under which they were provided to you ("License"). Unless the License provides otherwise, you may not use, modify, copy, publish, distribute, disclose or transmit this software or the related documents without Intel's prior written permission.

This software and the related documents are provided as is, with no express or implied warranties, other than those that are expressly stated in the License.

**Optimization Notice:** Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessors-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice. Notice Revision #20110804

Unless stated otherwise, the code examples in this document are provided to you under an MIT license, the terms of which are as follows:

Copyright 2019 Intel Corporation

Permission is hereby granted, free of charge, to any person obtaining a copy of this software and associated documentation files (the "Software"), to deal in the Software without restriction, including without limitation the rights to use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of the Software, and to permit persons to whom the Software is furnished to do so, subject to the following conditions:

The above copyright notice and this permission notice shall be included in all copies or substantial portions of the Software.

THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

# Contents

| 1 | Introdu          | ction                           |

|---|------------------|---------------------------------|

|   | 1.1 one          | API Programming Model Overview8 |

|   | 1.1.1            | Data Parallel C++ (DPC++)       |

|   | 1.1.2            | oneAPI Toolkit Distribution     |

|   | 1.2 Abc          | out This Guide                  |

|   | 1.3 Rela         | ated Documentation11            |

| 2 | oneAPI           | Programming Model               |

|   | 2.1 Sam          | 12 nple Program                 |

|   | 2.2 Plat         | form Model                      |

|   | 2.3 Exe          | cution Model                    |

|   | 2.4 Me           | 20 mory Model                   |

|   | 2.4.1            | Memory Objects                  |

|   | 2.4.2            | Accessors                       |

|   | 2.4.3            | Synchronization                 |

|   | 2.4.4            | Unified Shared Memory24         |

|   | 2.5 Ker          | nel Programming Model24         |

|   | 2.5.1            | C++ Language Requirements25     |

|   | 2.5.2            | Error Handling27                |

|   | 2.5.3            | Fall Back27                     |

| 3 | Progran          | nming Interface                 |

|   | 3.1 Sing         | gle Source Compilation          |

|   | 3.2 Con          | npiler Drivers                  |

|   | 3.3 Exa          | mple Compilation29              |

|   | 3.3.1            | API-Based Code                  |

|   | 3.3.2            | Direct Programming32            |

|   | 3.4 Con          | npilation Model                 |

|   | 3.4.1            | Compile to Object Step34        |

|   | 3.4.2            | Link to Executable Step         |

|   | 3.4.3            | Execute Step                    |

|   | 3.4.4            | Online Compilation              |

|   | 3.5 CPL          | J Flow                          |

|   | 3.5.1            | Example CPU Commands            |

|   | 3.5.2            | Online Compilation              |

|   | 3.5.3            | Offline Compilation             |

|   | 3.5.4            | Optimization Flags              |

|   | 3.5.5            | Host and Kernel Interaction     |

|   | 2.0 001          | J Flow                          |

|   | 3.6 GPU<br>3.6.1 | Example GPU Commands            |

#### Introduction

|   |     | 3.6.2    | Offline Compilation                                 | .39 |

|---|-----|----------|-----------------------------------------------------|-----|

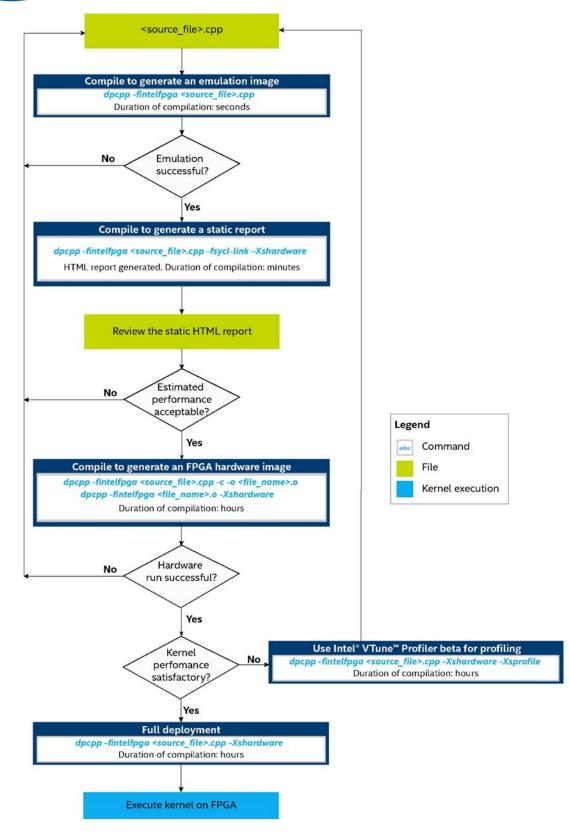

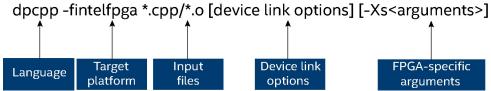

|   | 3.7 | FPGA     | A Flow                                              | .39 |

|   |     | 3.7.1    | Example FPGA Commands                               | .41 |

|   |     | 3.7.2    | Offline Compilation                                 | .41 |

|   |     | 3.7.3    | Targeting Multiple FPGAs                            | .46 |

|   |     | 3.7.4    | Other Supported Intel oneAPI DPC++ Compiler Options | .47 |

|   |     | 3.7.5    | FPGA Device Selection in the Host Code              | .47 |

|   |     | 3.7.6    | Host and Kernel Interaction                         | .48 |

|   |     | 3.7.7    | FPGA Workflows in IDEs                              | .49 |

|   | 3.8 | Com      | plex Scenario: Use of Static Libraries              | .49 |

|   |     | 3.8.1    | Create the Static Library                           | .49 |

|   |     | 3.8.2    | Use the Static Library                              | .49 |

|   | 3.9 | Stan     | dard Intel oneAPI DPC++ Compiler Options            | .49 |

| 4 |     | Data Par | allel C++ (DPC++) Programming Language and Runtime  | .52 |

| - | 4.1 |          | Version Support                                     |     |

|   | 4.2 |          | der Files and Namespaces                            |     |

|   | 4.3 |          | ++ Classes, Class Templates, & Defines              |     |

|   | 1.5 | 4.3.1    | Accessor                                            |     |

|   |     | 4.3.2    | Atomic                                              |     |

|   |     | 4.3.3    | Buffer                                              |     |

|   |     | 4.3.4    | Command Group Handler                               |     |

|   |     | 4.3.5    | Context                                             |     |

|   |     | 4.3.6    | Device                                              |     |

|   |     | 4.3.7    | Device Event                                        |     |

|   |     | 4.3.8    | Device Selector                                     |     |

|   |     | 4.3.9    | Event                                               |     |

|   |     | 4.3.10   | Exception                                           |     |

|   |     | 4.3.11   | Group                                               | .60 |

|   |     | 4.3.12   | ID                                                  | .60 |

|   |     | 4.3.13   | Image                                               | .61 |

|   |     | 4.3.14   | Item                                                | .61 |

|   |     | 4.3.15   | Kernel                                              | .61 |

|   |     | 4.3.16   | Multi-pointer                                       | .62 |

|   |     | 4.3.17   | Nd_item                                             | .62 |

|   |     | 4.3.18   | Nd_range                                            | .63 |

|   |     | 4.3.19   | Platform                                            | .63 |

|   |     | 4.3.20   | Program                                             | .64 |

|   |     | 4.3.21   | Queue                                               | .64 |

|   |     | 4.3.22   | Range                                               | .64 |

|   |     | 4.3.23   | Stream                                              | .65 |

|   |     | 4.3.24   | Vec and Swizzled Vec                                | .65 |

|   |     | 4.3.25   | Built-in Types & Functions                          | .65 |

|   |     | 4.3.26   | Property Interface                                  | 66  |

|---|-----|----------|-----------------------------------------------------|-----|

|   |     | 4.3.27   | Standard Library Classes Required for the Interface | 66  |

|   |     | 4.3.28   | Version                                             | 66  |

|   | 4.4 | Men      | nory Types                                          | 67  |

|   | 4.5 | Кеуч     | vords                                               | .67 |

|   | 4.6 | Prep     | rocessor Directives and Macros                      | .67 |

| 5 |     | API-base | ed Programming                                      | 68  |

|   | 5.1 | one      | API Library Overview                                | .68 |

|   | 5.2 | Intel    | oneAPI DPC++ Library (oneDPL)                       | .68 |

|   |     | 5.2.1    | oneDPL Library Usage                                | 69  |

|   |     | 5.2.2    | oneDPL Code Samples                                 | 69  |

|   | 5.3 | Intel    | oneAPI Math Kernel Library (oneMKL)                 | .72 |

|   |     | 5.3.1    | oneMKL Usage                                        | 72  |

|   |     | 5.3.2    | oneMKL Code Sample                                  | 73  |

|   | 5.4 | Intel    | oneAPI Threading Building Blocks (oneTBB)           | .77 |

|   |     | 5.4.1    | oneTBB Usage                                        | 77  |

|   |     | 5.4.2    | oneTBB Code Sample                                  |     |

|   | 5.5 | Intel    | oneAPI Data Analytics Library (oneDAL)              |     |

|   |     | 5.5.1    | oneDAL Usage                                        |     |

|   |     | 5.5.2    | oneDAL Code Sample                                  |     |

|   | 5.6 |          | oneAPI Collective Communications Library (oneCCL)   |     |

|   |     | 5.6.1    | oneCCL Usage                                        |     |

|   |     | 5.6.2    | oneCCL Code Sample                                  |     |

|   | 5.7 |          | oneAPI Deep Neural Network Library (oneDNN)         |     |

|   |     | 5.7.1    | oneDNN Usage                                        |     |

|   |     | 5.7.2    | oneDNN Code Sample                                  |     |

|   | 5.8 |          | oneAPI Video Processing Library (oneVPL)            |     |

|   |     | 5.8.1    | oneVPL Usage                                        |     |

|   | г о | 5.8.2    | oneVPL Code Sample                                  |     |

|   | 5.9 | Othe     | er Libraries                                        | .85 |

| 6 |     |          | Povelopment Process                                 |     |

|   | 6.1 | Perf     | ormance Tuning Cycle                                | .86 |

|   |     | 6.1.1    | Establish Baseline                                  |     |

|   |     | 6.1.2    | Identify Kernels to Offload                         |     |

|   |     | 6.1.3    | Offload Kernels                                     |     |

|   |     | 6.1.4    | Optimize                                            |     |

|   |     | 6.1.5    | Recompile, Run, Profile, and Repeat                 |     |

|   | 6.2 |          | Jgging                                              |     |

|   |     | 6.2.1    | Debugger Features                                   |     |

|   |     | 6.2.2    | SIMD Support                                        |     |

|   |     | 6.2.3    | Operating System Differences                        | 90  |

#### Introduction

|     | 6.2.4    | Environment Setup                         | 90   |

|-----|----------|-------------------------------------------|------|

|     | 6.2.5    | Breakpoints                               | 91   |

|     | 6.2.6    | Evaluations and Data Races                |      |

|     | 6.2.7    | Linux Sample Session                      | 91   |

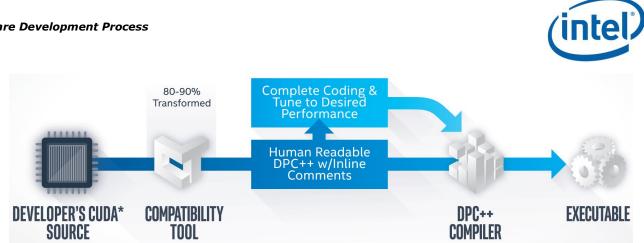

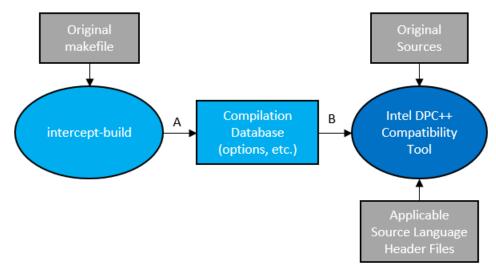

| 6.3 | Migr     | ating Code to DPC++                       | 94   |

|     | 6.3.1    | Migrating from C++ to SYCL/DPC++          | 94   |

|     | 6.3.2    | Migrating from CUDA* to DPC++             | 94   |

|     | 6.3.3    | Migrating from OpenCL Code to DPC++       | 96   |

|     | 6.3.4    | Migrating Between CPU, GPU, and FPGA      | 96   |

| 6.4 | Com      | posability                                | 99   |

|     | 6.4.1    | Compatibility with Other Compilers        | 99   |

|     | 6.4.2    | OpenMP* Offload Interoperability          |      |

|     | 6.4.3    | OpenCL <sup>™</sup> Code Interoperability |      |

| 7   | Glossary |                                           | .101 |

# **1** Introduction

Obtaining high compute performance on today's modern computer architectures requires code that is optimized, power efficient, and scalable. The demand for high performance continues to increase due to needs in AI, video analytics, data analytics, as well as in traditional high performance computing (HPC).

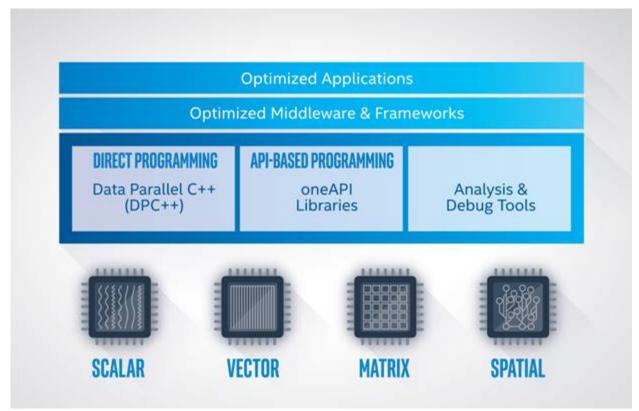

Modern workload diversity has resulted in a need for architectural diversity; no single architecture is best for every workload. A mix of scalar, vector, matrix, and spatial (SVMS) architectures deployed in CPU, GPU, AI, and FPGA **accelerators** is required to extract the needed performance.

Today, coding for CPUs and accelerators requires different languages, libraries, and tools. That means each hardware platform requires completely separate software investments and provides limited application code reusability across different target architectures.

The oneAPI programming model simplifies the programming of CPUs and accelerators using modern C++ features to express parallelism with a programming language called Data Parallel C++ (DPC++). The DPC++ language enables code reuse for the host (such as a CPU) and accelerators (such as a GPU) using a single source language, with execution and memory dependencies clearly communicated. Mapping within the DPC++ code can be used to transition the application to run on the hardware, or set of hardware, that best accelerates the workload. A host is available to simplify development and debugging of device code, even on platforms that do not have an accelerator available.

**NOTE:** Not all programs can benefit from the single programming model offered by oneAPI. It is important to understand if your program can benefit and how to design, implement, and use the model for your program.

## **1.1 oneAPI Programming Model Overview**

The oneAPI programming model provides a comprehensive and unified portfolio of developer tools that can be used across hardware targets, including a range of performance libraries spanning several workload domains. The libraries include functions custom-coded for each target architecture, so the same function call delivers optimized performance across supported architectures. DPC++ is based on industry standards and open specifications to encourage ecosystem collaboration and innovation.

As shown in the figure above, applications that take advantage of the oneAPI programming model can execute on multiple target hardware platforms ranging from CPU to FPGA. The oneAPI product is comprised of the Intel® oneAPI Base Toolkit and several add-on toolkits featuring complementary tools based on specific developer workload needs. The Intel oneAPI Base Toolkit includes the Intel® oneAPI DPC++ Compatibility Tool, select libraries, and analysis tools.

- Developers who want to migrate existing CUDA\* code to DPC++, can use the Intel DPC++ Compatibility Tool to help migrate their existing projects to DPC++.

- The Intel oneAPI DPC++ Compiler supports direct programming of code targeting accelerators. Direct programming is coding for performance when APIs are not available. It supports online and offline compilation for CPU and GPU targets and offline compilation for FPGA targets.

- API-based programming is supported via sets of optimized libraries. The library functions provided in the oneAPI product are pre-tuned for use with any supported target architecture, eliminating the need for developer intervention. For example, the BLAS routine available from **Intel oneAPI Math Kernel Library** is just as optimized for a GPU target as a CPU target.

- Finally, the compiled DPC++ application can be analyzed and debugged to ensure performance, stability, and energy efficiency goals are achieved using tools such as Intel<sup>®</sup> VTune<sup>™</sup> Profiler or Intel<sup>®</sup> Advisor.

### 1.1.1 Data Parallel C++ (DPC++)

Data Parallel C++ (DPC++) is a high-level language designed for data parallel programming productivity. It is based on C++ for broad compatibility and uses common, familiar C and C++ constructs. The

language seeks to deliver performance on par with other compiled languages, such as standard C++ compiled code, and uses C++ class libraries to allow the compiler to interpret the code and run on various supported architectures.

DPC++ is based on SYCL\* from the Khronos\* Group to support data parallelism and heterogeneous programming. In addition, Intel is pursuing extensions to SYCL with the aim of providing value to customer code and working with the standards organization for adoption. For instance, the DPC++ language includes an implementation of unified shared memory to ease memory usage between the host and the accelerators. These features are being driven into a future version of the SYCL language. For more details about SYCL, refer to version 1.2.1 of the SYCL Specification.

While DPC++ applications can run on any supported target hardware, tuning is required to gain the best performance advantage on a given target architecture. For example, code tuned for a CPU likely will not run as fast on a GPU accelerator without modification. This guide aims to help developers understand how to program using the oneAPI programming model and how to target and optimize for the appropriate architecture to achieve optimal application performance.

## 1.1.2 oneAPI Toolkit Distribution

oneAPI Toolkits are available via multiple distribution channels:

- Local product installation: install the oneAPI toolkits from the Intel® Developer Zone.

- Install from containers or repositories: install the oneAPI toolkits from one of several supported containers or repositories.

- Pre-installed in the Intel<sup>®</sup> DevCloud: use a free development sandbox for access to the latest Intel SVMS hardware and select oneAPI tools.

# **1.2 About This Guide**

This document provides:

- Chapter 2: An introduction to the oneAPI programming model (platform, execution, memory, and kernel programming)

- Chapter 3: Details about how to compile code for various accelerators (CPU, FPGA, etc.)

- Chapter 4: A description of the programming model with specifics about the Data Parallel C++ (DPC++) language options

- Chapter 5: A brief introduction to common APIs and related libraries

- Chapter 6: An overview of the software development process using various oneAPI tools, such as debuggers and performance analyzers, and optimizing code for a specific accelerator (CPU, FPGA, etc.)

# **1.3 Related Documentation**

The following documents are useful starting points for developers getting started with oneAPI projects. This document assumes you already have a basic understanding of the oneAPI programming model concepts.

Get Started with oneAPI for Linux\*

Get Started with oneAPI for Windows\*

oneAPI Release Notes

SYCL\* Specification (for version 1.2.1)

# 2 oneAPI Programming Model

The oneAPI programming model is based upon the SYCL\* Specification. The specification presents a general heterogeneous compute capability by detailing four models. These models categorize the actions a developer needs to perform to employ one or more devices as an accelerator. Aspects of these models appear in every program that employs the **oneAPI programming model**. These models are summarized as:

- Platform model Specifies the host and device(s).

- Execution model Specifies the **command queues** and issuing commands for execution on the device(s).

- Memory model Defines how the host and devices interact with memory.

- Kernel model Defines the code that executes on the device(s). This code is known as the kernel.

The programming language for oneAPI is Data Parallel C++ (DPC++) and employs modern features of the C++ language to enact its parallelism. In fact, when writing programs that employ the oneAPI programming model, the programmer routinely uses language features such as C++ lambdas, templates, parallel\_for, and closures.

**TIP:** If you are unfamiliar with these C++11 and later language features, consult other C++ language references and gain a basic understanding before continuing.

When evaluating and learning oneAPI, keep in mind that the programming model is general enough to accommodate multiple classes of accelerators; therefore, there may be a greater number of API calls required to access the accelerators than more constrained APIs, such as those only accessing one type of accelerator.

One of the primary motivations for DPC++ is to provide a higher-level programming language than OpenCL<sup>™</sup> C code, which it is based upon. Readers familiar with OpenCL programs will see many similarities to and differences from OpenCL code. This chapter points out similarities and differences where appropriate. This chapter also points to portions of the SYCL Specification for further information.

# 2.1 Sample Program

The following code sample contains a program that employs the oneAPI programming model to compute a vector addition. The program computes the formula c = a + b across arrays, a and b, each containing 1024 elements, and places the result in array c. The following discussion focusses on sections of code identified by line number in the sample. The intent with this discussion is to highlight the required functionality inherent when employing the programming model.

**NOTE:** Keep in mind that this sample code is intended to illustrate the four models that comprise the oneAPI programming model; it is not intended to be a typical program or the simplest in nature.

1 #include <vector>

2 #include <CL/sycl.hpp>

3

```

4

#define SIZE 1024

5

6 namespace sycl = cl::sycl;

7

8 int main() {

9

std::array<int, SIZE> a, b, c;

10

11

for (int i = 0; i<SIZE; ++i) {

12

a[i] = i;

13

b[i] = -i;

c[i] = i;

14

15

}

16

17

{

18

sycl::range<1> a size{SIZE};

19

20

auto platforms = sycl::platform::get platforms();

21

22

for (auto &platform : platforms) {

23

24

std::cout << "Platform: "</pre>

25

<< platform.get info<sycl::info::platform::name>()

26

<< std::endl;

27

28

29

auto devices = platform.get devices();

30

for (auto &device : devices ) {

31

std::cout << " Device: "</pre>

32

<< device.get info<sycl::info::device::name>()

33

<< std::endl;

34

}

35

36

}

37

38

sycl::default selector device selector;

39

sycl::queue d queue(device selector);

40

41

sycl::buffer<int, 1> a device(a.data(), a size);

42

sycl::buffer<int, 1> b device(b.data(), a size);

43

sycl::buffer<int, 1> c device(c.data(), a size);

44

45

d queue.submit([&](sycl::handler &cgh) {

46

auto c res =

c device.get access<sycl::access::mode::write>(cgh);

47

auto a in =

a device.get access<sycl::access::mode::read>(cgh);

```

```

48

auto b in =

b device.get access<sycl::access::mode::read>(cgh);

49

50

cgh.parallel for<class ex1>(a size,[=](sycl::id<1> idx) {

51

c_res[idx] = a_in[idx] + b_in[idx];

52

});

53

54

});

55

56

}

57 }

```

A DPC++ program has the **single source** property, which means the **host code** and the **device code** can be placed in the same file so that the compiler treats them as the same compilation unit. This can potentially result in performance optimizations across the boundary between host and device code. The single source property differs from a programming model like OpenCL software technology where the host code and device code are typically in different files, and the host and device compiler are different entities, which means no optimization can occur between the host and device code boundary. Therefore, when scrutinizing a DPC++ program, the first step is to understand the delineation between host code and device code. To be more specific, DPC++ programs are delineated into different scopes similar to programming language scope, which is typically expressed via { and } in many languages.

The three types of scope in a DPC++ program include:

- Application scope Code that executes on the host

- Command group scope Code that acts as the interface between the host and device

- Kernel scope Code that executes on the device

In this example, command group scope comprises lines 45 through 54 and includes coordination and data passing operations required in the program to enact control and communication between the host and the device.

| 45 | d_queue.submit([&](sycl::handler &cgh) {                                                                 |

|----|----------------------------------------------------------------------------------------------------------|

| 46 | <pre>auto c_res = c_device.get_access<sycl::access::mode::write>(cgh);</sycl::access::mode::write></pre> |

| 47 | <pre>auto a_in = a_device.get_access<sycl::access::mode::read>(cgh);</sycl::access::mode::read></pre>    |

| 48 | <pre>auto b_in = b_device.get_access<sycl::access::mode::read>(cgh);</sycl::access::mode::read></pre>    |

| 49 |                                                                                                          |

| 50 | cgh.parallel_for <class exl="">(a_size,[=](sycl::id<l> idx) {</l></class>                                |

| 51 | <pre>c_res[idx] = a_in[idx] + b_in[idx];</pre>                                                           |

| 52 | <pre>});</pre>                                                                                           |

| 53 |                                                                                                          |

| 54 | <pre>});</pre>                                                                                           |

Kernel scope, which is nested in the command group scope, comprises lines 50 to 52. Application scope consists of all the other lines not in command group or kernel scope. Syntactically, definitions are included from the top level include file; sycl.hpp and namespace declarations can be added for convenience.

The function of each of the lines and its classification into one of the four models are detailed as follows:

• Lines 2 and 6 – include and namespace – programs employing the oneAPI programming model require the include of cl/sycl.hpp. It is recommended to employ the namespace statement at line 6 to save typing repeated references into the cl::sycl namespace.

```

2 #include <CL/sycl.hpp>

3

4 #define SIZE 1024

5

6 namespace sycl = cl::sycl;

```

Lines 20 to 36 – Platform model – programs employing the oneAPI programming model can query the host for available platforms and can either select one to employ for execution or allow the oneAPI runtime to choose a default platform. A platform defines the relationship between the host and device(s). The platform may have a number of devices associated with it and a program can specify which device(s) to employ for execution or allow the oneAPI runtime to choose a default device.

| 20 | <pre>auto platforms = sycl::platform::get_platforms();</pre>                     |

|----|----------------------------------------------------------------------------------|

| 21 |                                                                                  |

| 22 | for (auto &platform : platforms) {                                               |

| 23 |                                                                                  |

| 24 | <pre>std::cout &lt;&lt; "Platform: "</pre>                                       |

| 25 | << platform.get_info <sycl::info::platform::name>()</sycl::info::platform::name> |

| 26 | << std::endl;                                                                    |

| 27 |                                                                                  |

| 28 |                                                                                  |

| 29 | <pre>auto devices = platform.get_devices();</pre>                                |

| 30 | for (auto &device : devices ) {                                                  |

| 31 | <pre>std::cout &lt;&lt; " Device: "</pre>                                        |

| 32 | << device.get_info <sycl::info::device::name>()</sycl::info::device::name>       |

| 33 | << std::endl;                                                                    |

| 34 | }                                                                                |

| 35 |                                                                                  |

| 36 | }                                                                                |

|    |                                                                                  |

• Lines 39 and 45 – Execution model – programs employing the oneAPI programming model define command queues that issue command groups. The command groups control execution on the device.

```

39 sycl::queue d_queue(device_selector);

40

41 sycl::buffer<int, l> a_device(a.data(), a_size);

42 sycl::buffer<int, l> b_device(b.data(), a_size);

43 sycl::buffer<int, l> c_device(c.data(), a_size);

44

45 d_queue.submit([&](sycl::handler &cgh) {

```

Lines 41 to 43 and lines 46 to 48 – Memory model – programs employing the oneAPI programming model may use buffers and accessors to manage memory access between the host and devices. In this example, the arrays, a, b, and c are defined and allocated on the host. Buffers, a\_device, b\_device, and c\_device, are declared to hold the values from a, b, and c respectively so the device can compute the vector addition. The accessors, a\_in and b\_in, denote that a\_device and b\_device are to have read only access on the device. The accessor c\_res denotes that c\_device is to allow write access from the device.

```

41 sycl::buffer<int, l> a_device(a.data(), a_size);

42 sycl::buffer<int, l> b_device(b.data(), a_size);

43 sycl::buffer<int, l> c_device(c.data(), a_size);

44

45 d_queue.submit([&](sycl::handler &cgh) {

46 auto c_res = c_device.get_access<sycl::access::mode::write>(cgh);

47 auto a_in = a_device.get_access<sycl::access::mode::read>(cgh);

48 auto b_in = b_device.get_access<sycl::access::mode::read>(cgh);

41 auto b_in = b_device.get_access<sycl::access::mode::read>(cgh);

42 auto b_in = b_device.get_access<sycl::access::mode::read>(cgh);

```

• Line 50 to 52 – Kernel Programming Model – The C++ language parallel\_for statement denotes that the code enclosed in its scope will execute in parallel across the **compute elements** of the device. This example code employs a C++ lambda to represent the kernel.

• Line 17 and 56 – Scope and Synchronization – Memory operations between the buffers and actual host memory execute in an asynchronous fashion. To ensure synchronization, the command queue is placed inside another scope at line 17 and 56 which tells the runtime to synchronize before the scope is exited as part of the buffer's destructors being executed. This practice is used in many programs.

When compiled and executed, the sample program computes the 1024 element vector add in parallel on the accelerator. This assumes the accelerator has multiple compute elements capable of executing in parallel. This sample illustrates the models that the software developer will need to employ in their program. The next sections discuss in more details those four models: the Platform model, the Execution model, the Memory model, and the Kernel model.

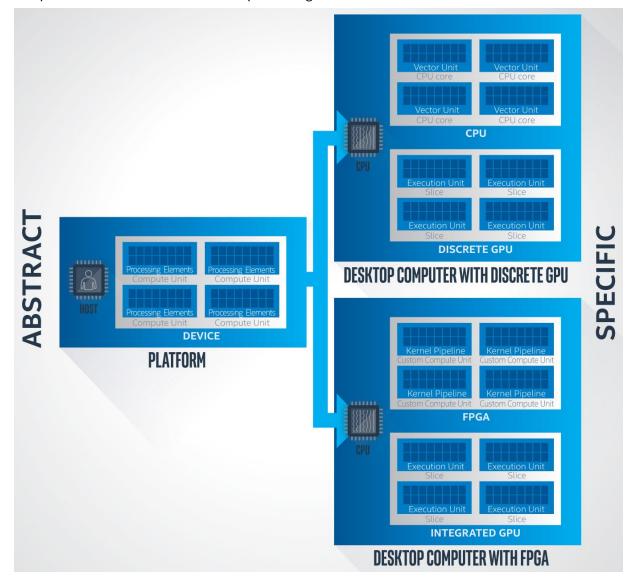

# 2.2 Platform Model

The platform model for oneAPI is based upon the SYCL\* platform model. It specifies a host controlling one or more devices. A host is the computer, typically a CPU-based system executing the primary portion of a program, specifically the application scope and the command group scope. The host coordinates and controls the compute work that is performed on the devices. A device is an accelerator, a specialized component containing compute resources that can quickly execute a subset of operations typically more efficiently than the CPUs in the system. Each device contains one or more compute units that can execute several operations in parallel. Each compute unit contains one or more **processing elements** that serve as the individual engine for computation.

A system can instantiate and execute several platforms simultaneously, which is desirable because a particular platform may only target a subset of the available hardware resources on a system. However,

in the typical case, a system will have one platform comprised of one or more supported devices, and the compute resources made available by those devices.

The following figure provides a visual depiction of the relationships in the platform model. One host communicates with one or more devices. Each device can contain one or more compute units. Each compute unit can contain one or more processing elements.

The platform model is general enough to be mapped to several different types of devices and lends to the functional portability of the programming model. The hierarchy on the device is also general and can be mapped to several different types of accelerators from FPGAs to GPUs and ASICs as long as these devices support the minimal requirements of the oneAPI programming model. Consult the oneAPI Release Notes for more information.

# **2.3 Execution Model**

The execution model is based upon the SYCL\* execution model. It defines and specifies how code, termed kernels, execute on the host and the devices.

The host execution model coordinates execution and data management between the host and devices via command groups. The command groups, which are groupings of commands like kernel invocation and accessors, are submitted to queues for execution. Accessors, which are formally part of the memory model, also communicate ordering requirements of execution. A program employing the execution model declares and instantiates queues. Queues can execute with an in-order or out-of-order policy controllable by the program. In-order execution is an Intel extension.

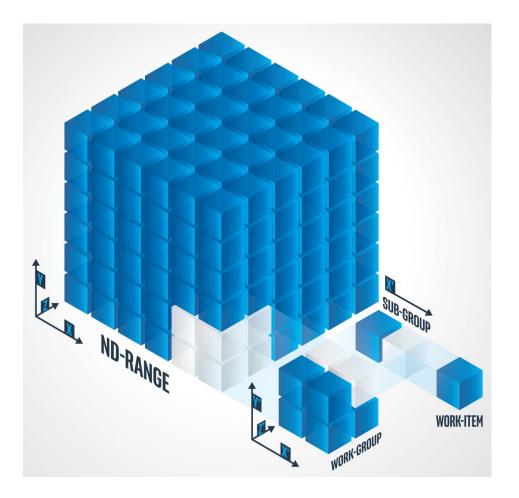

The device execution model specifies how computation is accomplished on the accelerator. Compute ranging from small one-dimensional data to large multidimensional data sets are allocated across a hierarchy of **ND-ranges**, **work-groups**, **sub-groups** (Intel extension), and **work-items**, which are all specified when the work is submitted to the command queue. It is important to note that the actual kernel code represents the work that is executed for one work-item. The code outside of the kernel controls just how much parallelism is executed; the amount and distribution of the work is controlled by specification of the sizes of the ND-range and work-group.

The following figure depicts the relationship between an ND-range, work-group, sub-group, and workitem. The total amount of work is specified by the ND-range size. The grouping of the work is specified by the work-group size. The example shows the ND-range size of X \* Y \* Z, work-group size of X' \* Y' \* Z', and subgroup size of X'. Therefore, there are X \* Y \* Z work-items. There are (X \* Y \* Z) / (X \* Y \* Z) / (X' \* Y' \* Z')Y' \* Z') work-groups and (X \* Y \* Z) / X' subgroups. oneAPI Programming Model

When kernels are executed, the location of a particular work-item in the larger ND-range, work-group, or sub-group is important. For example, if the work-item is assigned to compute on specific pieces of data, a method of specification is necessary. Unique identification of the work-item is provided via intrinsic functions such as those in the nd item class (global id, work group id, and local id).

The following code sample launches a kernel and displays the relationships of the previously discussed ND-range, work-group, and work-item.

```

1

#include<CL/sycl.hpp>

2

#include<iostream>

3

#define N 6

4

#define M 2

5

using namespace cl::sycl;

6

int main()

7

{

8

queue defaultqueue;

9

buffer<int,2> buf(range<2>(N,N));

10

defaultqueue.submit([&](handler &cgh){

11

auto bufacc = buf.get access<access::mode::read write>(cgh);

```

```

12

cgh.parallel for<class ndim>(nd range<2>(range<2>(N,N),

13

range<2>(M,M)), [=] (nd item<2> i) {

14

id<2> ind = i.get global id();

15

bufacc[ind[0]][ind[1]] = ind[0]+ind[1];

16

});

17

});

18

auto bufacc1 = buf.get access<access::mode::read>();

19

for(int i = 0; i < N; i++) {

20

for(int j = 0; j < N; j++)</pre>

21

std::cout<<bufacc1[i][j]<<"\t";</pre>

22

std::cout<<"\n";</pre>

23 }

24

return 0;

25 }

```

#### **ND-Range Parallelism Example**

The following discusses the relationships in the use of the ND-range in the previous code sample.

- At line 12 is the nd-range declaration. nd range<2> specifies a two-dimensional index space.

- The global range is specified by the first argument, range<2>(N,N), which specifies the overall index space as 2 dimensions with size N by N.

- The second argument, range<2> (M, M) specifies the local work-group range as 2 dimensions with size M by M.

- Line 13 employs nd\_item<2> to reference each work-item in the ND-range, and calls get global id to determine the index in the global buffer, bufacc.

The sub-group is an extension to the SYCL execution model and sits hierarchically between the work\_group and work\_item. The sub\_group was created to align with typical hardware resources that contain a vector unit to execute several similar operations in parallel and in lock step.

## 2.4 Memory Model

The memory model for oneAPI is based upon the SYCL\* memory model. It defines how the host and devices interact with memory. It coordinates the allocation and management of memory between the host and devices. The memory model is an abstraction that aims to generalize across and be adaptable to the different possible host and device configurations. In this model, memory resides upon and is owned by either the host or the device and is specified by declaring a memory object. There are two different types of memory objects, **buffers** and **images**. Interaction of these memory objects between the host and device is accomplished via an **accessor**, which communicates the desired location of access, such as host or device, and the particular mode of access, such as read or write.

Consider a case where memory is allocated on the host through a traditional malloc call. Once the memory is allocated on the host, a buffer object is created, which enables the host allocated memory to be communicated to the device. The buffer class communicates the type and number of items of that type to be communicated to the device for computation. Once a buffer is created on the host, the type of access allowed on the device is communicated via an accessor object, which specifies the type of access to the buffer. The general steps are summarized as:

1. Instantiate a buffer or image object.

The host or device memory for the buffer or image is allocated as part of the instantiation or is wrapped around previously allocated memory on the host.

2. Instantiate an accessor object.

The accessor specifies the required location of access, such as host or device, and the particular mode of access, such as read or write. It represents dependencies between uses of memory objects. The following code sample is exercising different memory objects and accessors.

```

1 #include <vector>

2 #include <CL/sycl.hpp>

3 namespace sycl = cl::sycl;

4

5 #define SIZE 64

6

7 int main() {

8

std::array<int, SIZE> a, c;

9

std::array<sycl::float4, SIZE> b;

10 for (int i = 0; i<SIZE; ++i) {

11

a[i] = i;

12

b[i] = (float) - i;

13

c[i] = i;

14

}

15

16

{

17

sycl::range<1> a size{SIZE};

18

19

sycl::queue d queue;

20

21

sycl::buffer<int> a device(a.data(), a size);

22

sycl::buffer<int> c device(c.data(), a size);

23

sycl::image<2>

b device(b.data(),sycl::image channel order::rgba,

24

sycl::image channel type::fp32, sycl::range<2>(8, 8));

25

26

d queue.submit([&](sycl::handler &cgh) {

27

sycl::accessor<int, 1, sycl::access::mode::discard write,</pre>

28

sycl::access::target::global buffer> c res(c device, cgh);

29

sycl::accessor<int, 1, sycl::access::mode::read,</pre>

30

sycl::access::target::constant buffer> a res(a device, cgh);

31

sycl::accessor<sycl::float4, 2, sycl::access::mode::write,</pre>

32

sycl::access::target::image> b res(b device, cgh);

33

34

sycl::float4 init = {0.f, 0.f, 0.f, 0.f};

35

cgh.parallel for<class ex1>(a size, [=] (sycl::id<1> idx) {

36

```

- Lines 8 and 9 contain the host allocations of arrays a, b, & c. The declaration of b is as a float4 because it will be accessed as an image on the device side.

- Lines 27 and 28 create an accessor for c\_device that has an access mode of discard\_write and a target of global\_buffer.

- Lines 29 and 30 create an accessor for a\_device that has an access mode of read and a target of constant\_buffer.

- Lines 31 and 32 create an accessor for <code>b\_device</code> that has an access mode of <code>write</code> and a target of image.

The accessors specify where and how the kernel will access these memory objects. The runtime is responsible for placing the memory objects in the correct location. Therefore, the runtime may copy data between host and device to meet the semantics of the accessor target.

Designate accessor targets to optimize the locality of access for a particular algorithm. For example, specify that local memory should be employed if much of the kernel access would benefit from memory that resides closer to the processing elements.

If the kernel attempts to violate the communicated accessor by either attempting to write on a read accessor or read on a write accessor, a compiler diagnostic is emitted. Not all combinations of access targets and access modes are compatible. For details, see the SYCL Specification.

### 2.4.1 Memory Objects

Memory objects are either buffers or images.

- Buffer object a one-, two-, or three-dimensional array of elements. Buffers can be accessed via lower level C++ pointer types. For further information on buffers, see the SYCL Specification.

- Image object a formatted opaque memory object stored in a type specific and optimized fashion. Access occurs through built-in functions. Image objects typically pertain to pictures comprised of pixels stored in a format such as RGB (red, green, blue intensity). For further information on images, see the SYCL Specification.

### 2.4.2 Accessors

Accessors provide access to buffers and images in the host or inside the kernel and also communicate data dependencies between the application and different kernels. The accessor communicates the data type, the size, the target, and the access mode. To enable good performance, pay particular attention to the target because the accessor specifies the memory type from the choices in the SYCL memory model.

The targets associated with buffers are:

- global\_buffer

- host\_buffer

- constant\_buffer

- local

The targets associated with images are:

- image

- host image

- image\_array

Image access must also specify a channel order to communicate the format of the data being read. For example, an image may be specified as a float4, but accessed with a channel order of RGBA.

The access mode impacts correctness as well as performance and is one of read, write, read\_write, discard\_read\_write, or atomic. Mismatches in access mode and actual memory operations such as a write to a buffer with access mode read can result in compiler diagnostics as well as erroneous program state. The discard\_write and discard\_read\_write access modes can provide performance benefits for some implementations. For further details on accessors, see the SYCL Specification.

### 2.4.3 Synchronization

It is possible to access a buffer without employing an accessor, however it should be the rare case. To do so safely, a mutex\_class should be passed when a buffer is instantiated. For further details on this method, see the SYCL Specification.

| Target          | Description                                                                              |

|-----------------|------------------------------------------------------------------------------------------|

| host_buffer     | Access the buffer on the host.                                                           |

| global_buffer   | Access the buffer through global memory on the device.                                   |

| constant_buffer | Access the buffer from constant memory on the device. This may enable some optimization. |

| local           | Access the buffer from local memory on the device.                                       |

| image           | Access the image                                                                         |

| image_array     | Access an array of images                                                                |

| host_image      | Access the image on the host.                                                            |

#### Access targets

#### Access modes

| Memory Access Mode | Description                                    |

|--------------------|------------------------------------------------|

| read               | Read-only                                      |

| write              | Write-only                                     |

| read_write         | Read and write                                 |

| discard_write      | Write-only access. Previous value is discarded |

| discard_read_write | Read and write. Previous value is discarded    |

| atomic             | Provide atomic, one at a time, access.         |

### 2.4.4 Unified Shared Memory

An extension to the standard SYCL memory model is unified shared memory, which enables the sharing of memory between the host and device without explicit accessors in the source code. Instead, manage access and enforces dependences with explicit functions to wait on events or signaling a depends\_on relationship between events.

Another characteristic of unified shared memory is that it provides a C++ pointer-based alternative to the buffer programming model. Unified shared memory provides both explicit and implicit models for managing memory. In the explicit model, programmers are responsible for specifying when data should be copied between memory allocations on the host and allocations on a device. In the implicit model, the underlying runtime and device drivers are responsible for automatically migrating memory between the host and a device. Since unified shared memory does not rely on accessors, dependences between operations must be specified using events. Programmers may either explicitly wait on event objects or use the depends\_on method inside a command group to specify a list of events that must complete before a task may begin.

# 2.5 Kernel Programming Model

The kernel programming model for oneAPI is based upon the SYCL\* kernel programming model. It enables explicit parallelism between the host and device. The parallelism is explicit in the sense that the programmer determines what code executes on the host and device; it is not automatic. The kernel code executes on the accelerator. Programs employing the oneAPI programming model support single source, meaning the host code and device code can be in the same source file. However, there are differences between the source code accepted in the host code and the device code with respect to language conformance and language features. The SYCL Specification defines in detail the required language features for host code and device code. The following is a summary that is specific to the oneAPI product.

### 2.5.1 C++ Language Requirements

The host code can be compiled by C++11 and later compilers and take advantage of supported C++11 and later language features. The device code requires a compiler that accepts all C++03 language features and the following C++11 features:

- Lamdba expressions

- Variadic templates

- Alias templates

- rvalue references

- std::function, std::string, std::vector

In addition, the device code cannot use the following features:

- Virtual Functions

- Virtual Inheritance

- Exceptions handling throws and catches between host and device

- Run Time Type Information (RTTI)

- Object management employing new and delete operators

The device code is specified via one of three language constructs: lambda expression, functor, or kernel class. The separation of host code and device code via these language constructs is natural and accomplished without language extensions. These different forms of expressing kernels give the developer flexibility in enmeshing the host code and device code. For example:

- To put the kernel code in line with the host code, consider employing a lambda expression.

- To have the device code separate from the host code, but still maintain the single source property, consider employing a functor.

- To port code from OpenCL programs or to ensure a more rigid separation between host and device code, consider employing the kernel class.

The Device code inside a lambda expression, functor, or kernel object can then specify the amount of parallelism to request through several mechanisms.

- single\_task execute a single instance of the kernel with a single work item.

- parallel\_for execute a kernel in parallel across a range of processing elements. Typically, this version of parallel\_for is employed on "embarrassingly parallel" workloads.

- parallel\_for\_work\_group execute a kernel in parallel across a hierarchical range of processing elements using local memory and barriers.

The following code sample shows two combinations of invoking kernels:

- 1. single\_task and C++ lambda (lines 33-40)

- 2. parallel\_for and functor (lines 8-20 and line 50)

These constructs enclose the aforementioned kernel scope. For details, see the SYCL Specification.

```

1 #include <vector>

2 #include <CL/sycl.hpp>

3

4 #define SIZE 1024

5

6 namespace sycl = cl::sycl;

```

```

7

8

template <typename T> class Vassign {

9

T val;

10

sycl::accessor<T, 1, sycl::access::mode::read write,</pre>

11

sycl::access::target::global buffer> access;

12

13 public:

Vassign(T val , sycl::accessor<T, 1,</pre>

14

sycl::access::mode::read write,

15

sycl::access::target::global buffer> &access ) :

val(val),

16

access(access) {}

17

18 void operator()(sycl::id<1> id) { access[id] = 1; }

19

20 };

21

22 int main() {

23

std::array<int, SIZE> a;

24

25

for (int i = 0; i<SIZE; ++i) {

26

a[i] = i;

27

}

28

{

29

sycl::range<1> a size{SIZE};

30

sycl::buffer<int, 1> a device(a.data(), a size);

31

sycl::queue d queue;

32

33

d queue.submit([&](sycl::handler &cgh) {

34

auto a in =

a device.get access<sycl::access::mode::write>(cgh);

35

36

cgh.single task<class ex1>([=]() {

37

a in[0] = 2;

38

});

39

});

40

}

41

42

{

43

sycl::range<1> a size{SIZE};

sycl::buffer<int, 1> a device(a.data(), a size);

44

45

sycl::queue d queue;

46

d queue.submit([&](sycl::handler &cgh) {

47

auto a in =

a device.get access<sycl::access::mode::read write,

48

sycl::access::target::global buffer>(cgh);

```

```

49 Vassign<int> F(0, a_in);

50 cgh.parallel_for(sycl::range<1>(SIZE), F);

51 });

52 }

53 }

```

### 2.5.2 Error Handling

C++ exception handling is the basis for handling error conditions in the programming model. Some restrictions on exceptions are in place due to the asynchronous nature of host and device execution. For example, it is not possible to throw an exception in kernel scope and catch it (in the traditional sense) in application scope. Instead, there are a set of restrictions and expectations in place when performing error handling. These include:

- At application scope, the full C++ exception handling mechanisms and capability are valid as long as there is no expectation that exceptions can cross to kernel scope.

- At the command group scope, exceptions are asynchronous with respect to the application scope. During command group construction, an <u>async\_handler</u> can be declared to handle any exceptions occurring during execution in the command group.

For further details on error handling, see the SYCL Specification.

### 2.5.3 Fall Back

Typically, a command group is submitted and executed on the designated command queue; however, there may be cases where the command queue is unable to execute the group. In these cases, it is possible to specify a fall back command queue for the command group to be executed upon. This capability is handled by the runtime. This fallback mechanism is detailed in the SYCL Specification.

The following code fails due to the size of the workgroup when executed on Intel Processor Graphics, such as Intel HD Graphics 530. The SYCL specification allows specifying a secondary queue as a parameter to the submit function and this secondary queue is used if the device kernel runs into issues with submission to the first device.

```

#include<CL/sycl.hpp>

1

2

#include<iostream>

3

#define N 1024

#define M 32

4

5

using namespace cl::sycl;

6

int main() {

7

{

8

cpu selector cpuSelector;

9

queue cpuQueue(cpuSelector);

10 queue defaultqueue;

11 buffer<int,2> buf(range<2>(N,N));

12 defaultqueue.submit([&](handler &cgh){

13

auto bufacc = buf.get access<access::mode::read write>(cgh);

14

cqh.parallel for<class ndim>(nd range<2>(range<2>(N,N),

```

```

15 range<2>(M,M)), [=](nd item<2> i){

16 id<2> ind = i.get_global_id();

17 bufacc[ind[0]][ind[1]] = ind[0]+ind[1];

18 });

19 },cpuQueue);

20 auto bufacc1 = buf.get_access<access::mode::read>();

21 for(int i = 0; i < N; i++) {

22 for(int j = 0; j < N; j++){

23 if(bufacc1[i][j] != i+j){

24

std::cout<<"Wrong result\n";</pre>

25

return 1;

26 }

27 }

28 }

29 std::cout<<"Correct results\n";</pre>

30 return 0;

31 }

32 }

```

# **3** Programming Interface

This chapter details the oneAPI compilation process across direct programming and API-based programming covering CPU, GPUs, and FPGAs. Some details about the tools employed at each stage of compilation are explained.

# **3.1 Single Source Compilation**

The oneAPI programming model supports single source compilation. Single source compilation has several benefits compared to separate host and device code compilation. It should be noted that the oneAPI programming model also supports separate host and device code compilation as some users may prefer it. Advantages of the single source compilation model include:

- Usability programmers need to create fewer files and can define device code right next to the call site in the host code.

- Extra safety single source means one compiler can see the boundary code between host and device and the actual parameters generated by host compiler will match formal parameters of the kernel generated by the device compiler.

- Optimization the device compiler can perform additional optimizations by knowing the context from which a kernel is invoked. For instance, the compiler may propagate some constants, infer pointer aliasing information across the function call.

# **3.2 Compiler Drivers**

The Intel oneAPI DPC++ Compiler includes two compiler drivers:

- dpcpp is a GCC\* compatible compiler driver. It recognizes GCC-style command line options (starting with "-") and can be useful for projects that share a build system across multiple operating systems.

- dpcpp-cl is a Microsoft\* Visual C++ compatible driver. This driver is only available on Windows. It

recognizes Windows command line options (starting with "/") and can be useful for Microsoft Visual

Studio\*-based projects.

The examples in this guide use the dpcpp driver.

# 3.3 Example Compilation

The oneAPI tools are available in several convenient forms, as detailed in oneAPI Toolkit Distribution earlier in this guide. Follow the instructions in the Installation Guide to obtain and install the tools. Once the tools are installed and the environment is set, compile code for execution.

## 3.3.1 API-Based Code

The following code shows usage of an API call (a \* x + y) employing the Intel oneAPI Math Kernel Library function mkl::blas::axpy to multiply a times x and add y across vectors of floating point numbers. It takes advantage of the oneAPI programming model to perform the addition on an accelerator.

```

1 #include <vector> // std::vector()

2 #include <cstdlib> // std::rand()

3 #include <CL/sycl.hpp>

4 #include "mkl sycl.hpp"

5

6 int main(int argc, char* argv[]) {

7

8

double alpha = 2.0;

9

int n elements = 1024;

10

11

int incx = 1;

12

std::vector<double> x;

13

x.resize(incx * n elements);

for (int i=0; i<n elements; i++)</pre>

14

15

x[i*incx] = 4.0 * double(std::rand()) / RAND MAX - 2.0;

// rand value between -2.0 and 2.0

16

17

18

int incy = 3;

19

std::vector<double> y;

y.resize(incy * n elements);

20

21

for (int i=0; i<n elements; i++)</pre>

22

y[i*incy] = 4.0 * double(std::rand()) / RAND MAX - 2.0;

23

// rand value between -2.0 and 2.0

24

25

cl::sycl::device my dev;

26

try {

27

my dev = cl::sycl::device(cl::sycl::gpu selector());

28

} catch (...) {

29

std::cout << "Warning, failed at selecting qpu device.</pre>

30

Continuing on default(host) device." << std::endl;

31

}

32

33

// Catch asynchronous exceptions

34

auto exception handler = [] (cl::sycl::exception list

35

exceptions) {

36

for (std::exception ptr const& e : exceptions) {

37

try {

38

std::rethrow exception(e);

39

} catch(cl::sycl::exception const& e) {

40

std::cout << "Caught asynchronous SYCL</pre>

```

#### Programming Interface

```

41

exception:\n"

42

<< e.what() << std::endl;

43

}

44

}

45

};

46

47

cl::sycl::queue my queue(my dev, exception handler);

48

49

cl::sycl::buffer<double, 1> x buffer(x.data(), x.size());

50

cl::sycl::buffer<double, 1> y buffer(y.data(), y.size());

51

52

// perform y = alpha * x + y

53

try {

54

mkl::blas::axpy(my queue, n elements, alpha, x buffer,

55

incx, y buffer, incy);

56

}

57

catch(cl::sycl::exception const& e) {

58

std::cout << "\t\tCaught synchronous SYCL exception:\n"</pre>

59

<< e.what() << std::endl;

60

}

61

// copy y buffer data back to y vector

62

63

auto y accessor = y buffer.template

64

get access<cl::sycl::access::mode::read>();

65

for (int i=0; i<y.size(); ++i)</pre>

66

y[i] = y accessor[i];

67

std::cout << "The axpy (y = alpha * x + y) computation is</pre>

68

69

complete!" << std::endl;</pre>

70

71

return 0;

72 }

```

To compile and build the application:

- Ensure that the MKLROOT environment variable is set appropriately (echo \${MKLROOT}). If it is

not set appropriately, run the setvars.sh or setvars.bat script or set the variable to the folder

that contains the lib and include folders. For more information about the setvars.sh script,

see Get Started with Intel oneAPI Toolkits for Linux\* or Get Started with Intel oneAPI Toolkits for

Windows\*.

- 2. Build the application using the following command:

dpcpp -I\${MKLROOT}/include -Icommon -DMKL\_ILP64 -w -c axpy.cpp -o axpy.o

3. Link the application using the following command:

```

dpcpp -I${MKLROOT}/include -DMKL_ILP64 -w axpy.o -foffload-static-

lib="${MKLROOT}/lib/intel64"/libmkl_sycl.a -Wl,-export-dynamic -Wl,--start-

group "${MKLROOT}/lib/intel64"/libmkl_intel_ilp64.a

"${MKLROOT}/lib/intel64"/libmkl sequential.a

```

```

"${MKLROOT}/lib/intel64"/libmkl_core.a -Wl,--end-group -lsycl -lpthread -lm -

ldl -o axpy.out

```

```

4. Run the application using the following command:

```

./axpy.out

## 3.3.2 Direct Programming

The vector addition sample code is employed in this example. It takes advantage of the oneAPI programming model to perform the addition on an accelerator.

The following command compiles and links the executable.

```

dpcpp vector add.cpp

```

The components and function of the command and options are similar to those discussed in the API-Based Code section.

Execution of this command results in the creation of an executable file, which performs the vector addition when run.

# **3.4 Compilation Model**

The command used to compile a program employing the oneAPI programming model is very similar to standard C/C++ compilation with standard compile and link steps. However, the compilation model supports code that executes on both a host and potentially several accelerators simultaneously. Thus, the commands issued by the compiler, linker, and other supporting tools as a result of compile and link steps are more complicated than standard C/C++ compilation targeting one architecture. The developer is protected from this complexity; however advanced users of the tools may want to understand these details to better target specific architectures.

A DPC++ program can consist of a set of source files, where each may have both host and device code. Compilation of the host code is somewhat straightforward as the target architecture is known. Typically, the host is an x86-based computer.

By default, the Intel oneAPI DPC++ Compiler compiles device code into a device-agnostic form that can run on any compatible devices. This is known as online compilation because the device-agnostic code gets compiled into a device-specific form at runtime, or when "online." Additionally, DPC++ allows production of device-specific code at compile time. This process is known as offline compilation. Offline compilation for devices presents several challenges because of the need to target several architectures, some known and some unknown at the time of compilation. In addition, it may be helpful to apply aggressive optimization to a specific target. The compilation model supports these different needs. The compilation model enables:

- Target specific code Target specific versions of a kernel function

- Target specific optimization Compiler optimization for a specific target

- General target support Target a broad set of architectures

- Future target support Target a new architecture. This could be the case in forward compatibility cases where a new architecture provides new optimization opportunities.

#### **Programming Interface**

To support these needs, the code can be compiled into two main forms – a **SPIR-V** intermediate representation, which is the device-agnostic form, and target specific executable code.

- The SPIR-V representation enables online compilation, which is compilation to device code at execution time.

- Compilation to target specific executable code before executing the application is termed offline compilation. The Intel oneAPI DPC++ Compiler creates multiple code forms for each device.

These two forms are bundled together in an application binary known as a **fat binary**. The fat binary is employed by the oneAPI runtime when the application executed and form needed for the target device is determined at runtime. Device code for multiple devices co-exists in a single fat binary.

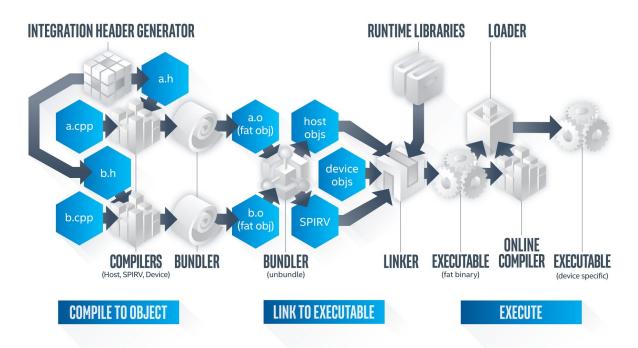

The following figure illustrates the compilation process from source code to fat binary.

The tools participating in the compilation are represented by rectangles in the figure and are described as follows:

- **Driver** The executable name is dpcpp on Linux\* and dpcpp-cl on Windows\*. Invoke this file on the command line to start compilation. It orchestrates the compilation process and invokes other tools as needed.

- **Host compiler** the DPC++ host compiler. It is possible to employ a third-party host compiler by invoking the tools manually.

- **Device compiler** a DPC++ device compiler (there can be more than one), SPIR-V compiler by default. The output files have the extension \*.bc. SPIR-V is produced after the device code linkage step.

- **SPIRV compiler llvm-spirv** standard LLVM tool distributed with the Intel<sup>®</sup> oneAPI Base Toolkit that converts LLVM IR bitcode to SPIR-V.

- Bundler Marshalls host and device object code into a single file called a fat object.

- **Unbundler** Unmarshalls fat objects back into their constituent host and device object code. It is a part of the bundler.

- LLVM bitcode linker standard LLVM tool distributed with the Intel<sup>®</sup> oneAPI Base Toolkit that links LLVM IR bitcode files.

- **<Target> Back End** a back end for the target <Target> used in the offline compilation scenario. Compiles SPIR-V to native device code form.

- **Platform linker** the standard linker on the development platform 1d on Linux and link.exe on Windows.

- **Offload wrapper** wraps device binaries (different from device object files) into a host object file linked with the final DPC++ executable (fat binary)

File Types:

- **Device object file** device object code suitable for further linkage with other device objects. Can be LLVM bitcode or some native ISA.

- Host object file usual object file containing host object code. Examples include COFF on Windows or ELF on Linux.

- **Fat object file** a host object format file containing host and device code compiled for all targets passed via -fsycl-targets. Device code is inserted into special object file sections.

- Fat binary file a host executable containing device binaries either in SPIR-V or other form.

The compilation is a three-step process:

- Compile to Object The source code in the files a.cpp and b.cpp is parsed into an intermediate representation. Optimizations are invoked on the intermediate representation. The compiler command line specifies a list of targets for device object code generation or the default SPIR-V can be used. These objects are bundled together into a fat object. Two fat objects are produced a.o and b.o (a.obj and b.obj on Windows)

- 2. Link to Executable The fat objects are unbundled and linked together into a target specific image and a generic image. Additional optimizations may be invoked during this phase. The target specific image and generic image are grouped together into a fat binary.

- 3. Execute The fat binary is loaded for execution. Once the program control flow arrives to the place where DPC++ kernel offload is invoked, the oneAPI runtime is called to determine if a target specific executable image exists. If it does, execution proceeds with the target specific executable image. If it does not, the generic image is loaded, which calls the compiler to create a target specific image from the SPIR-V image when the kernel is submitted. If neither of the two exist, then the kernel executes on the host. Execution of the user application portion of the fat binary proceeds.

The starting point for any compilation involves the invocation of the compiler driver, dpcpp. The following compilation command compiles two source files, a.cpp and b.cpp, compiles, and links them into an executable:

dpcpp a.cpp b.cpp

This is the simplest compilation scenario where compilation and linkage are done in one step and the device code is delivered in device-agnostic form. More complex scenarios are described later.

### 3.4.1 Compile to Object Step

During the compile to object step, the source files are compiled and the output is the fat objects - one per input source. To support single source compilation, an integration header file is created for each

source. In the compilation model figure above, these are named  $a \cdot h$  and  $b \cdot h$  respectively; however, in practice they will have a uniquely generated name to avoid conflict with any actual  $a \cdot h$  or  $b \cdot h$  file. The integration header enables the host code to invoke the device code and execute it on different devices with the necessary communication and coordination enabled through the oneAPI programming model.

Once the integration header is created, the compile to object step is performed by the appropriate compiler:

- Host Compiler The host code is compiled by the host compiler. The host compiler is set by default during installation. The output is an object file that represents the host code. It includes the integration header to interoperate with the device code.

- SPIR-V device compiler The device code is compiled by the SPIR-V compiler to generate a SPIR-V intermediate representation of the code. The output is a target-independent object file, which is a SPIR-V binary intermediate representation of the device code.

- Specific device compiler The device code is compiled by a specific device compiler to generate a target specific object file. This is part of an offline compilation scenario. The target is specified using the -Xsycl targets option.

Once the host object file and the specified target object files have been created, they are grouped together using the bundler tool into a fat object file. In the example command above, there is no specific device compiler employed; only the SPIR-V device compiler is invoked to create target independent object files. Note that when compilation and linkage are done in a single step, then no fat objects are created, thus avoiding bundling/unbundling overhead.

## 3.4.2 Link to Executable Step

The link to executable step transforms the fat object files into a fat binary. The actions taken during this step are very similar to the traditional link step of compiling for one target, such as x86:

- Object files are linked together, satisfying variable and function dependencies between the files

- Third-party library dependencies are satisfied by linking the specified libraries

- Compiler libraries and runtime routines are linked into the resulting executable.

There are some differences. Since the oneAPI programming model enables more devices to be employed and compilation to occur at more than one time, the additional steps employed during the link to executable step are as follows:

- Unbundling of the fat object files Multiple target-specific and generic SPIR-V object files are bundled during the compile to object step. These fat object files are unbundled so that the correct target specific and generic SPIR-V object files can be grouped together for linking.

- Offline compilation Compilation during the link to executable step can occur. This step is optional and is used in the offline compilation scenario.

The option to request offline compilation (for example, for the Intel Processor Graphics included in 6<sup>th</sup> Generation Intel Processors) at this step is:

```

dpcpp -fsycl-targets=spir64_gen-unknown-linux-sycldevice -Xsycl-target-

backend=spir64_gen-unknown-linux-sycldevice "-device skl" src1.cpp

src2.cpp

```

The process of compiling the linked generic SPIR-V device binary into a target image is repeated for every device requested.

• Fat binary – The resulting host code and potentially multiple device images are linked together into a fat binary. This is the resulting executable that executes on the host device and then selectively executes the device kernels on the appropriate devices. A generic SPIR-V image may be included in the fat binary for use during the online compilation step (default if offline compilation is not requested).

### 3.4.3 Execute Step

During the execute step, the fat binary is obtained and loaded onto the system for execution. The fat binary is an operating system module (an executable or a dynamically loaded library) containing one or more device code binaries.

When a DPC++ application starts, its operating system modules are loaded into the process memory, and static initialization is performed for each. During this static initialization process, each module makes a call into the DPC++ runtime to register available device binary images. The DPC++ runtime bookmarks the registered binaries and uses them to resolve kernel launch requests to the appropriate device kernels.

To target new devices, the oneAPI programming model supports online compilation. If a device code binary is not available during a kernel launch request, an online compilation may be requested.

DPC++ applications may also dynamically compile and run OpenCL kernels provided in the source form. The main APIs for this feature are:

- cl::sycl::program::build\_with\_source to dynamically create a kernel from a string containing OpenCL code.

- cl::sycl::program::get\_kernel to obtain the DPC++ kernel instance, which can be run on a device.

See the DPC++ Specification for more details about the APIs.

### 3.4.4 Online Compilation